12/10/2022

# مراجعة مفاهيم هامة

م. عبير ميا م. مصعب خباز

محتوى مجاني غير مخصص للبيع التجاري

## بنية الحاسوب 2

أعزاءنا الطلبة، سنكمل ما بدأنا بالتعلم عنه في مادة بنية الدواسب 1 ولكن سنقف أولاً في هذه المحاضرة لراجعي بعض المفاهيم الأساسية.

بشكل عام فإن المفاهيم الأساسية التي سيتم دراستها في هذا المقرر:

- تصميم Control Unit

- البناء السلمي الفائق S.S

- التوارد I.A

- الذاكرة الافتراضية

- الذاكرة الخالية

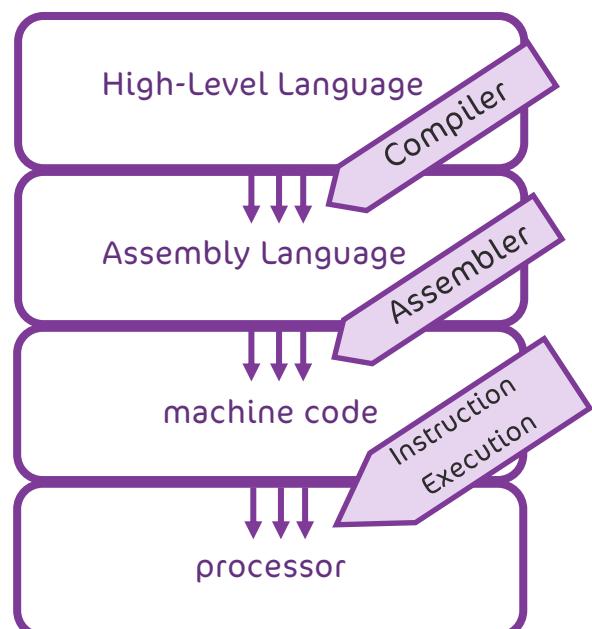

مستويات البرمجة والمراحل التي تتم بها

### High-level Languages

تتميز بأنها ذات معانٍ واضحة ومفهومة مثل:

Go To 20

وللانتقال من هذا المستوى إلى المستوى الأدنى تمر بالمرحلة التي تسمى Compiling والتي يكون Compiler هو المسؤول عنها وتتلخص هذه العملية بأنها تقوم بترجمة هذا الكود من High-level Language إلى Assembly Languages.

مثل: C++, Java, Perl, Haskell, Dart

محتوى مجاني غير مخصص للبيع التجاري

## Assembly Languages

- تتميز بأنها مفهومة نوعاً ما للمستخدم ولكن ليس لسابقتها، لأنها على مستوى أقل من التجريد (مثال: لغة MIPS).

- نجأ لاستخدامها أحياناً لكونها أقرب للآلية وللانتقال من هذا المستوى إلى المستوى الأدنى عبر المرحلة التي تسمى Assembling والتي يكون Assembler هو المسؤول عنها، تتلخص هذه العملية بأنها تقوم بترجمة هذا الكود من Assembly Language إلى Machine code أي (الأصفار والواحدات).

- بعد ذلك نصل إلى التنفيذ العملي على processor.

## ممر المعطيات Data Path وأنواعه

### 1. ممر المعطيات أحدى الدور Single Cycle

- كل تعليمة يتم تنفيذها في دور ساعة واحد.

### 2. متعدد الأدوار Multi-Cycle

- كل تعليمة يتم تنفيذها على عدة مراحل، كل مرحلة تتم في دور ساعة واحد.

### 3. المتوازد Pipelined

- يتم تنفيذ التعليمة على عدة مراحل، مع التداخل بين تنفيذ التعليمات.

## أنماط التعليمات MIPS instruction Formats

### R-type ( op = 0 )

| <i>op</i> | <i>rs</i> | <i>rt</i> | <i>rd</i> | <i>Shift</i> | <i>func</i> |

|-----------|-----------|-----------|-----------|--------------|-------------|

| 6 bits    | 5 bits    | 5 bits    | 5 bits    | 5 bits       | 6 bits      |

▪ من الشكل *add rd, rs, rt*

▪ مثال: *add \$9, \$8, \$7*

▪ منها التعليمات: add, sub, and, or

I-type ( $op \neq 0, 2, 3$ )

|           |           |           |                  |

|-----------|-----------|-----------|------------------|

| <i>op</i> | <i>rs</i> | <i>rt</i> | <i>immediate</i> |

| 6 bits    | 5 bits    | 5 bits    | 16 bits          |

من الشكل

مثال: *addi \$8,\$6,-1*

منها التعليمات: ...addi, andi, ori, lw, sw, beq, bne

J-type

|           |                                   |

|-----------|-----------------------------------|

| <i>op</i> | <i>Immediate (target address)</i> |

| 6 bits    | 26 bits                           |

من الشك

مثال: *j Label* ( $op = 2$ )

مثال: *jal Func* ( $op = 3$ )

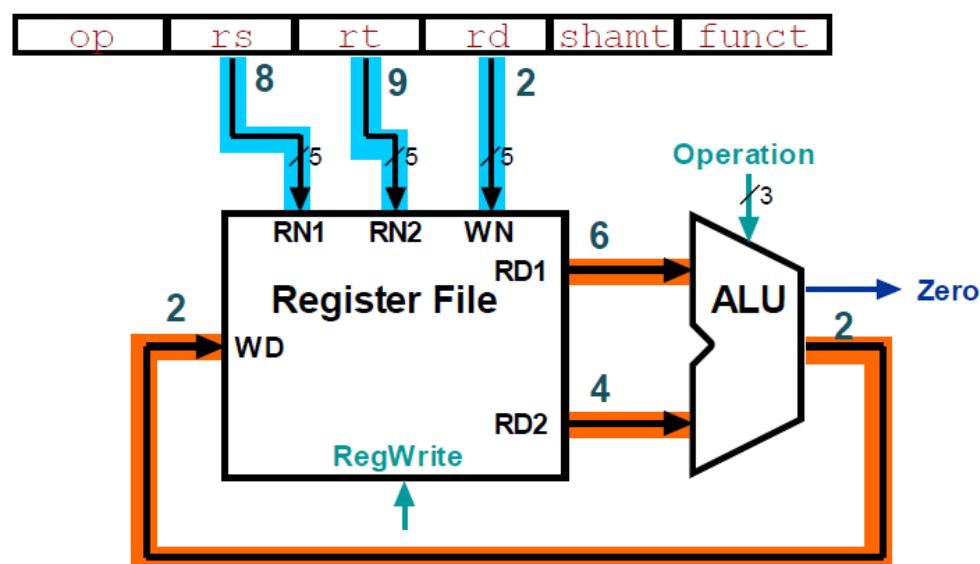

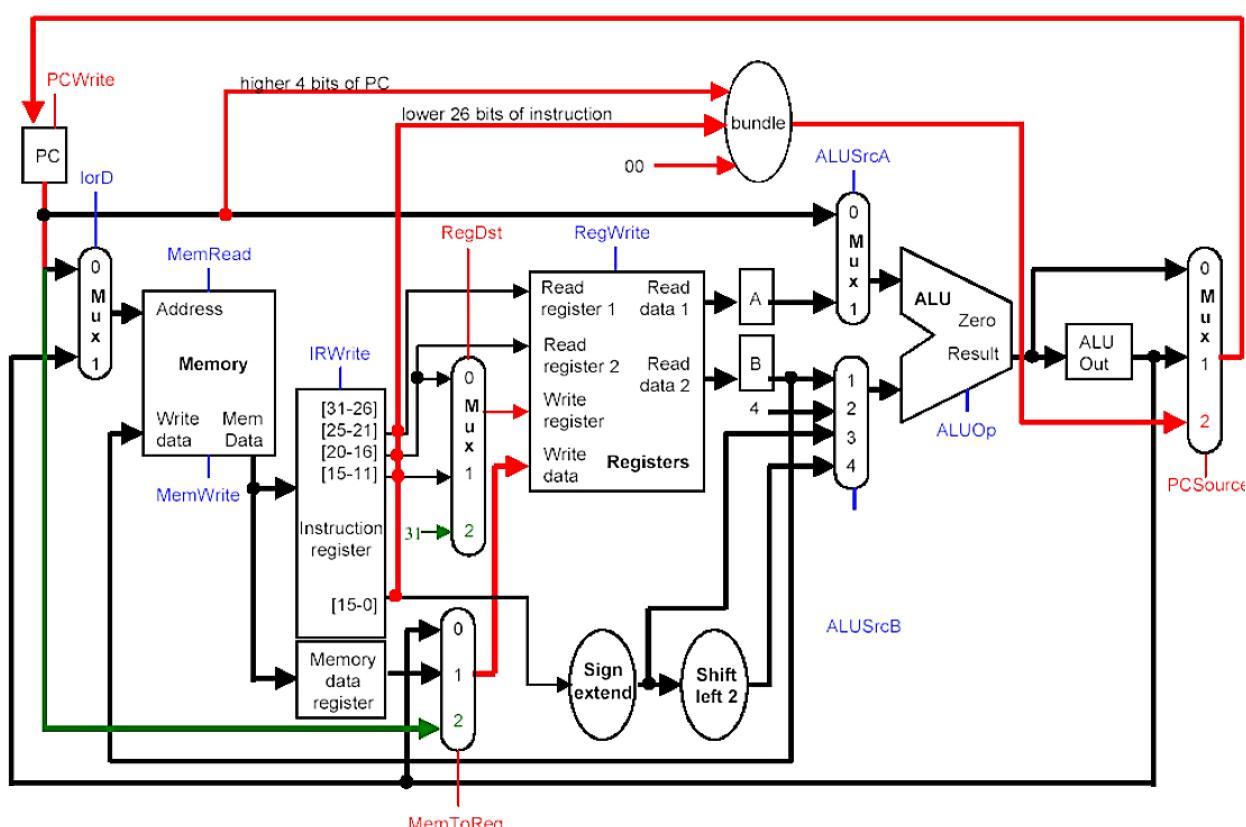

تعريف: حدد القيم العددية الموزعة على مفر المعطيات المرفق عند تنفيذ العملية التالية بفرض أن

$$\$8 = 6, \$9 = 4, \$2 = 1$$

*sub \$2,\$8,\$9 #* $\$2 \leftarrow \$8 - \$9 = 6 - 4 = 2$

*sub rd,rs,rt #* $rd \leftarrow rs - rt$

### Instruction

تمرين: بفرض لدينا المصفوفة الموضحة بالشكل، ما عمل البرنامج التالي، وما تحتوى الذاكرة النهائية؟

| Address    | Value (+0) | Value (+4) | Value (+8) | Value (+c) | Value (+10) | Value (+14) | Value (+18) | Value (+1c) |

|------------|------------|------------|------------|------------|-------------|-------------|-------------|-------------|

| 0x10010000 | 5          | 3          | 2          | 1          | 8           | 6           | 0           | 0           |

| 0x10010020 | 0          | 0          | 0          | 0          | 0           | 0           | 0           | 0           |

1. *addi \$s0,\$zero,10 #* \$s0 = 10 ( $s = 10$ )

2. *addi \$t1,\$zero,5 #* \$t1 = 5

3. *loop: lw \$t2,0(\$t0) # load x[i] in \$t2*

4. *add \$t2,\$t2,\$s0 #* \$t2 =  $x[i] + 10$

5. *sw \$t2,0(\$t0) # store \$t2 in x[i]*

6. *addi \$t0,\$t0,4 #* \$t2 = \$t2 + 4 (next  $x[ ]$ )

7. *addi \$t1,\$t1,-1 #* \$t1 = \$t1 - 1

8. *bne \$t1,\$zero,loop # last loop iteration reached?*

يقابل عمل الحلقة:

```

for (i = 5; i > 0; i = i - 1)

x[i] = x[i] + s;

```

| Address    | Value (+0) | Value (+4) | Value (+8) | Value (+c) | Value (+10) | Value (+14) | Value (+18) | Value (+1c) |

|------------|------------|------------|------------|------------|-------------|-------------|-------------|-------------|

| 0x10010000 | 15         | 13         | 12         | 11         | 18          | 6           | 0           | 0           |

| 0x10010020 | 0          | 0          | 0          | 0          | 0           | 0           | 0           | 0           |

أي أنه يقوم بزيادة أول 5 عناصر بمقدار 10

Average CPU performance

$$CPUtime = CC \cdot T = IC \cdot \frac{CPI}{f}$$

$f$  تردد المعالج  $f$

$IC$  عدد التعليمات في البرنامج

$CC$  عدد الأدوار الكلية في البرنامج

(Cycles Per Instruction) عدد الدورات(الوسطي) في التعليمية  $CPI$

### MIPS (Million instruction per second)

$$MIPS = \frac{IC}{CPUtime} \times 10^{-6}$$

### MFLOP (Million Floating Point Operations per second)

$$MFLOPS = \frac{N(FP\ operations)}{CPUtime} \times 10^{-6}$$

### Amdahl's Law

$$Speedup = \frac{performance(new)}{performance(old)} = \frac{CPUtime(old)}{CPUtime(new)}$$

تعرين : بفرض لدينا المعالجين التاليين P1, P2 ينفذان نفس مجموعة التعليمات، الأول معالج أحادي النبضة Single Cycle ، والآخر متعدد الأدوار Multi Cycle وفيه CPI=3 ويفعلان على ترددات الساعة الواردة بالجدول، المطلوب:

1. أيهما أعلى بقيمة MIPS ؟

↳ بفرض أن عدد التعليمات في البرنامج المنفذ = 3200 احسب زمن التنفيذ على المعالجين، واحسب عدد أدوار التنفيذ، وحدد أي المعالجين له الأداء الأعلى؟

1)  $CPI_1 = 1$

نعلم أن:  $MIPS = \frac{IC}{CPUtime} \times 10^{-6} = \frac{f}{CPI} * 10^{-6}$

$MIPS_{(1)} = 1.6 \cdot 10^9 \cdot 10^{-6} = 1.6 \times 10^3 = 1600$

| Processor | Clock rate (f)    | CPI |

|-----------|-------------------|-----|

| P1        | $1.6 \times 10^9$ | ?   |

| P2        | $2.4 \times 10^9$ | 3   |

$MIPS_{(2)} = \frac{2.4 \times 10^9}{3} \times 10^{-6} = 0.8 \times 10^3 = 800 \Rightarrow MIPS_{(1)} > MIPS_{(2)}$

2)  $MIPS = \frac{IC}{CPUtime} \times 10^{-6} \rightarrow CPUtime = \frac{IC}{MIPS} \times 10^{-6}$

$CPUtime_{(1)} = \frac{3200}{1600} \times 10^{-6} = 2 \times 10^{-6} (s) \quad CPUtime_{(2)} = \frac{3200}{800} \times 10^{-6} = 4 \times 10^{-6} (s)$

بما أن زمن التنفيذ على المعالج P1 أقل فهو ذو الأداء الأعلى في تنفيذ هذا البرنامج

$$CPUtime = \frac{CC}{f} \rightarrow CC = f \times CPUtime$$

$CC_{(1)} = 1.6 \cdot 10^9 \cdot 2 \cdot 10^{-6} = 3200 (\text{cycles})$

$CC_{(2)} = 9600 (\text{cycles})$

تمرين : بفرض أن لدينا برنامجاً يتألف من تشكيلاة التعليمات التالية:

650 ALU operations, 100 stores, 600 loads, 50 branches

وفرض أن كل تعليمة حسابية يلزمها 1 cycle، كل تعليمة تحميل أو تخزين في الذاكرة يلزمها 5 cycles .2 GHz، وبفرض أن تردد المعالج تعليمة تفرع يلزمها 2 cycles ، وبفرض أن تردد المعالج

1. احسب زمن التنفيذ .*CPI*

2. بفرض أمكننا تقليل عدد التعليمات التحميل إلى النصف، احسب التسريع الناتج، ثم احسب *CPI*<sub>new</sub>

$$1) \text{CPUtime} = \frac{CC}{f} = \frac{650 \times 1 + 100 \times 5 + 600 \times 5 + 50 \times 2}{2 \times 10^9} = \frac{4250}{2 \times 10^9} = 2125 \text{ (ns)}$$

$$CPI = \frac{CC}{IC} = \frac{4250}{1400} = 3.03$$

$$2) \text{CPUtime}_{\text{new}} = \frac{CC}{f} = \frac{650 \times 1 + 100 \times 5 + 300 \times 5 + 50 \times 2}{2 \times 10^9} = \frac{2750}{2 \times 10^9} = 1375 \text{ (ns)}$$

$$\text{Speedup} = \frac{\text{performance}_{\text{new}}}{\text{performance}_{\text{old}}} = \frac{\text{CPUtime}_{\text{old}}}{\text{CPUtime}_{\text{new}}} = \frac{2125 \text{ ns}}{1375 \text{ ns}} = 1.54$$

$$CPI_{\text{new}} = \frac{\text{CPUtime}_{\text{new}} \times f}{IC_{\text{new}}} = 1375n \times \frac{2G}{1100} = 2.5$$

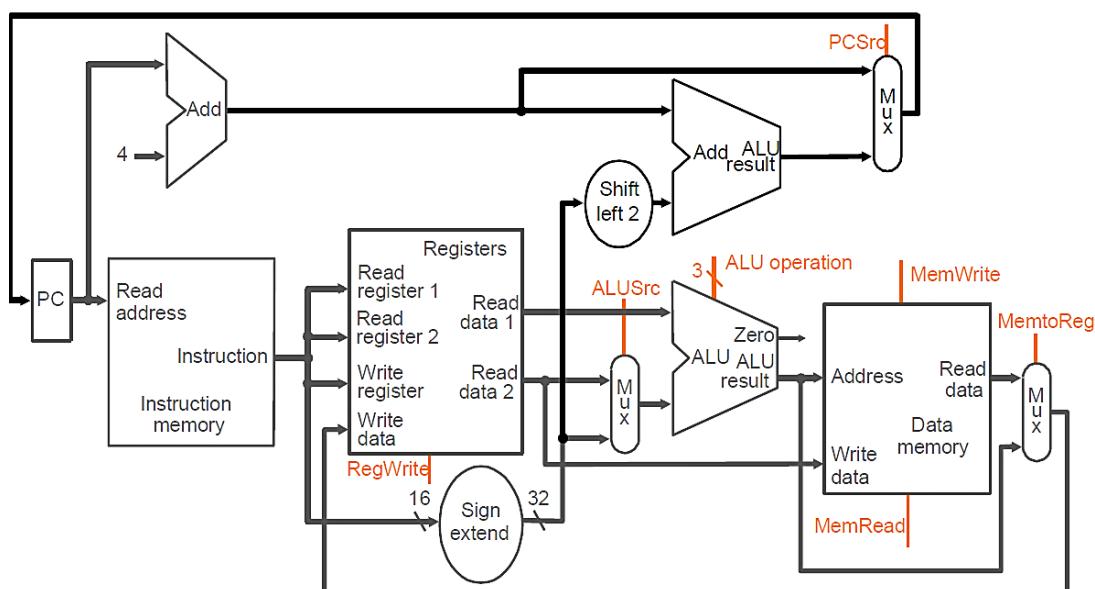

تمرين : بفرض لدينا ممر المعطيات التالي لمعالج MIPS أحادي الدور (Single Cycle DataPath) S.C

1. بفرض أنه يتم تنفيذ التعليمات التالية (*add, lw, sw, j*) ما هي قيمة *CPI*؟

2. احسب زمن دور المعالج بفرض أن أزمنة التأخير كالتالي:

Memory access = 10ns, Alu = 8 ns, Register file access = 5

2) زمن الدور حسب أطول تعليمة ينفذها المعالج وفي حالتنا (lw) فهو مجموع الأزمنة:

$$Mem + R.F + ALU + Mem + R.F = 10 + 5 + 8 + 10 + 5 = 38 \text{ (ns)}$$

تمرين : لدينا معر المعطيات التالي لمعالج MIPS متعدد الأدوار

1. بفرض أنه يتم تنفيذ تسلسل التعليمات التالية (add, lw, sw, j) ما هي قيمة CPI؟

2. احسب زمن دور المعالج بفرض أن أزمنة التأخير كالتالي:

Memory access=10 (ns), ALU = 8 (ns). Register file Access = 5

$$CPI = \frac{CC}{IC} = \frac{4+5+4+3}{4} = \frac{16}{4} = 4 \quad (1)$$

2) زمن الدور حسب أطول مرحلة يمر بها المعالج وفي حالتنا هي مرحلة الذاكرة فيكون:  $T = 10 \text{ (ns)}$

وظيفة: نريد اختبار مترجمين compilers 2 مختلفين على معالج يعمل بتردد 500 MHz، تم استخدام كل من المترجمين من أجل برنامج معين، فحصلنا على القيم الموضحة في الجدول، المطلوب: احسب CPI بالحالتين وأي التسلسليين أسرع بالتنفيذ؟

| Instruction Class | CPI | عدد التعليمات باستخدام المترجم الأول | عدد التعليمات باستخدام المترجم الثاني |

|-------------------|-----|--------------------------------------|---------------------------------------|

| A                 | 1   | $5 \times 10^6$                      | $7 \times 10^6$                       |

| B                 | 2   | $1 \times 10^6$                      | $1 \times 10^6$                       |

| C                 | 3   | $2 \times 10^6$                      | $1 \times 10^6$                       |

$$CPUtime = CC \cdot T = IC \cdot \frac{CPI}{f}$$

نعلم أن:

$$\rightarrow CC \cdot T = IC \cdot CPI \cdot T$$

$$CC = IC \cdot CPI$$

$$\Rightarrow CPI = \frac{CC}{IC}$$

$$CPI_{(1)} = \frac{1 \cdot (5 \cdot 10^6) + 2 \cdot (1 \cdot 10^6) + 3 \cdot (2 \cdot 10^6)}{(5 \cdot 10^6) + (1 \cdot 10^6) + (2 \cdot 10^6)}$$

$$= \frac{5 + 2 + 6}{5 + 1 + 2} = \frac{13}{8}$$

$$CPI_{(1)} = 1.625$$

$$CPI_{(2)} = \frac{1 \cdot (7 \cdot 10^6) + 2 \cdot (1 \cdot 10^6) + 3 \cdot (1 \cdot 10^6)}{(7 \cdot 10^6) + (1 \cdot 10^6) + (1 \cdot 10^6)}$$

$$= \frac{7 + 2 + 3}{9} = \frac{12}{9}$$

$$CPI_{(2)} = 1.33$$

لمعرفة أي التسلسليين أسرع نقارن زمن تنفيذهما:

$$\frac{CPUtime_1}{CPUtime_2} = \frac{\frac{IC_1 \cdot CPI_1}{f}}{\frac{IC_2 \cdot CPI_2}{f}} = \frac{8 \times 1.625}{9 \times 1.33} = \frac{13}{11.97}$$

$$\Rightarrow CPUtime_1 > CPUtime_2$$

ومنه نجد أن التسلسل الثاني أسرع

وظيفة: بفرض أن لدينا برنامجاً معيناً ينفذ على معالج A فيه تردد الساعة  $f = 200 \text{ MHz}$  ، فكان عدد التعليمات الكلي = 40 مليون تعليمية، و  $MIPS = 50$ . وعند تفريذه على معالج B ذي التردد  $f = 400 \text{ MHz}$  (باستخدام مترجم مختلف) كان عدد التعليمات الكلي = 60 مليون تعليمية، و  $CPI = 6$

1. احسب  $CPI$  في حالة المعالج A.

2. أي المعالجين أسرع في تنفيذ البرنامج وما نسبة التسريع؟

3. احسب قيمة  $MIPS$  في حالة المعالج B.

$$MIPS = \frac{IC \cdot 10^{-6}}{CPUtime} \Rightarrow CPUtime = \frac{IC}{MIPS} \times 10^6 \quad (1)$$

$$CPUtime_A = \frac{40 \times 10^6}{50} \times 10^{-6} = 0.8 \text{ (s)}$$

$$CPUtime = IC \times \frac{CPI}{f} \Rightarrow CPI = f \cdot \frac{CPUtime}{IC}$$

$$CPI_A = \frac{200 \cdot 10^6 \cdot 0.8}{40 \cdot 10^6}$$

$$\Rightarrow CPI_A = 4$$

(2) لحساب أي المعالجين أسرع نقارن زمن تنفيذهما:

$$\frac{CPUtime_A}{CPUtime_B} = \frac{0.8}{\frac{60 \times 10^6 \times 6}{400 \times 10^6}} = \frac{0.8}{0.9}$$

ومنه المعالج A أسرع من B في تنفيذ البرنامج بنسبة  $\frac{9}{8} = 1.125$

(3) بتطبيق القانون:

$$MIPS = \frac{IC}{CPUtime} \times 10^{-6}$$

$$\Rightarrow MIPS_B = \frac{60 \times 10^6}{0.9} \times 10^{-6} = 66.67$$

## نلقاء في المحاضرة القادمة