16/11/2022

# Pipelining التوارد

م. عبير ميا م. مصعب خبار

محظى مجاني غير مخصص للبيع التجاري

## بنية الحاسوب 2

تكلمنا في المحاضرات السابقة عن آلية تصميم ورسم وحدة التحكم Control Unit بالطريقة العتادية عن طريق معادلات إشارات التحكم. في هذه المحاضرة سنتحدث عن آلية عمل التعليمات بشكل متوازد في معالجات الـ MIPS وعلى أخطاء المعطيات Data Hazards وكيفية معالجتها برمجيا.

### Pipelining التوارد

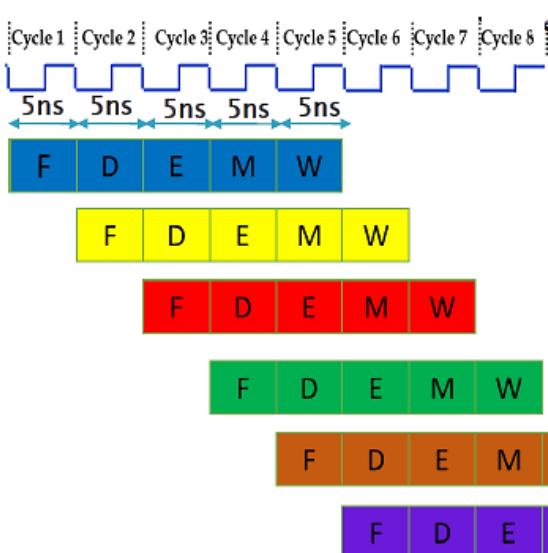

**تمرين 1:** بفرض معالج متوازد  $P.L$  مؤلف من 5 مراحل  $F, D, E, M, W$  وبفرض أن أ زمنة التأخير كال التالي:  $Regs = 2ns, Mem = 5ns, ALU = 3ns$ :

1. احسب زمن الدور الأصغرى، والتردد الأعظمى للمعالج

زمن الدور الأصغرى للمعالج يكون محدود ب زمن أبطأ مرحلة في التعليمية يمكن أخذها بحيث يكفي لتنفيذ جميع المراحل السابقة. وهنا نلاحظ أن كل من زمن جلب التعليمية من الذاكرة  $Mem$  والذي يرمز له ب  $F$  وزمن القراءة  $ALU$  والكتابة على الذاكرة  $Mem$  والتي يرمز لها ب  $M$  كليهما يعتمدان على زمن التأخير  $Mem = 5ns$ , وبالتالي هو زمن أبطأ مرحلة أي زمن الدور الأصغرى هو  $T = 5ns$ .

التعدد الأعظمي للمعالج يساوي إلى مقلوب زمن الدور الأصغرى

$$f = \frac{1}{T} = \frac{1}{5ns} = 200 MHz$$

2. عند تنفيذ برنامج مؤلف من 6 تعليمات، وبفرض عدم وجود أي نوع من الأعطال No Hazards، احسب كلاً من:  $CPU_{time}, CPI, CC$ .

يعطى قانون حساب عدد الأدوار الكلي لتنفيذ كامل العمليات بالعلاقة التالية

$$CC = P \cdot L \text{ depth} + (IC - 1) + stalls = 5 + 5 + 0 = 10 \text{ cycles}$$

حيث أن:  $P \cdot L \text{ Depth}$  هو عمق التوارد ويساوي إلى عدد مراحل تنفيذ التعليمة.

$IC$  هو عدد التعليمات الكلية للبرنامج.

$Stalls$  هو عدد التأخيرات الزمنية اللازم إضافتها لمنع حدوث  $hazards$  (يلزم إضافتها فقط في حال كان لدينا  $hazards$  في تنفيذ التعليمات وهنا لا يوجد لدينا  $hazards$  في المسألة).

$$CPI = \frac{CC}{IC} = \frac{10}{6} = 1.66$$

$$CPU_{time} = CC * T = 10 * 5 = 50ns$$

3. عند تنفيذ برنامج مؤلف من 1000000 تعليمية، وبفرض عدم وجود أي نوع من الأعطال، احسب  $CPI$ .

$$CPI = \frac{5+(IC-1)+stalls}{IC} = 1000004/1000000 = 1.000004 \approx 1$$

ملاحظة: كلما كانت الـ  $CPI$  قريبة من 1 كلما كان أداء المعالج أفضل ونلاحظ أنه عندما يكون عدد التعليمات كبير نسبياً يكون أداء المعالج أفضل أي أننا نستفاد من تقنية التوارد بشكل أكبر.

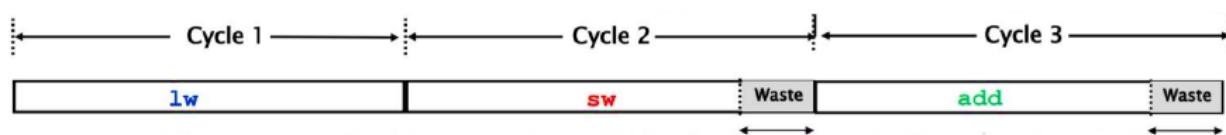

تمرين 2: بفرض تم تنفيذ 3 تعليمات هي  $lw, sw, add$  على ثلاثة معالجات: أحادي الدور  $SC$  فيه  $T = 5ns$ ، متعدد الأدوار  $MC$  فيه  $T = 1ns$ ، ومتواحد  $PL$  ذي 5 مراحل فيه  $5ns$  وبفرض عدم وجود أية أعطال، ما هو زمن التنفيذ بالحالات الثلاثة؟

1. في مسار المعطيات أحادي الدور *Single Cycle Data Path*

$$CPU_{time} = CC * T = 3 * 5 = 15ns$$

## 2. في مسار المعطيات متعدد الأدوار

$$CPU_{time} = CC * T = (5 + 4 + 4) * 1 = 13ns$$

## 3. في مسار المعطيات المتوازد

$$CPU_{time} = CC * T = (5 + 2) * 1 = 7ns$$

### توضيح

في مسار المعطيات أحدادي الدور يكون الدور بحسب أطول تعليمة سوف تنفذ بحيث كل تعليمة سوف تنتظر هذا الزمن بغض النظر عن طولها. علما أنه لا يمكن الانتقال للتعليمية التالية إلا عند الانتهاء من تنفيذ التعليمية الحالية. ويكون **عدد الأدوار الكلي هو أطول تعليمية × عدد التعليمات.**

في مسار المعطيات متعدد الأدوار تم تقسيم التعليمات إلى مراحل بحيث أصبح الدور هو زمن تنفيذ المراحل الواحدة ولا داعي أن تنتظر التعليمية أكبر دور في التعليمات. علما أنه لا يمكن الانتقال للتعليمية التالية إلا عند الانتهاء من تنفيذ التعليمية الحالية. ويكون **عدد الأدوار الكلي هو مجموع مراحل كل تعليمية.**

في مسار المعطيات المتوازد تم تقسيم عملية المعالجة إلى مراحل بحيث عند الانتهاء من مرحلة F مثلاً في تعليمية معينة يمكن البدء في نفس المرحلة للتعليمية القادمة دون الانتظار الانتهاء تنفيذ التعليمية الأولى. وهذا يمكن الانتقال للتعليمية التالية حال الانتهاء من مرحلة معينة، إذ يمكن بدء التعليمية التالية عند هذه المرحلة. ويكون **عدد الأدوار الكلي هو عمق التعليمية + عدد التعليمات - 1**

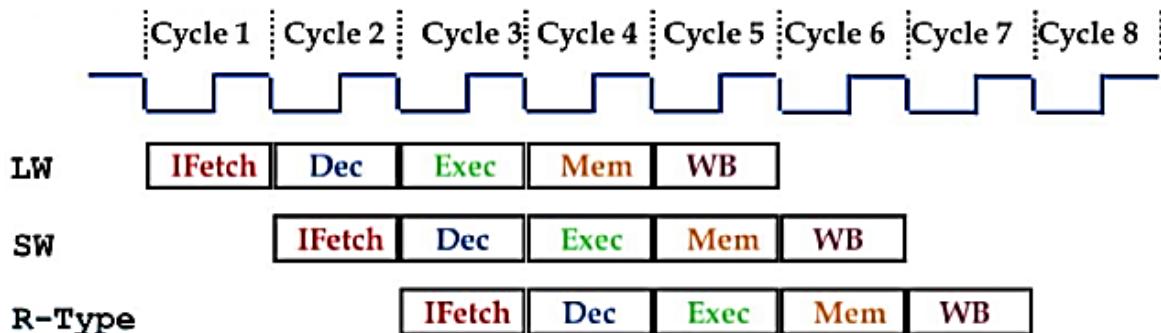

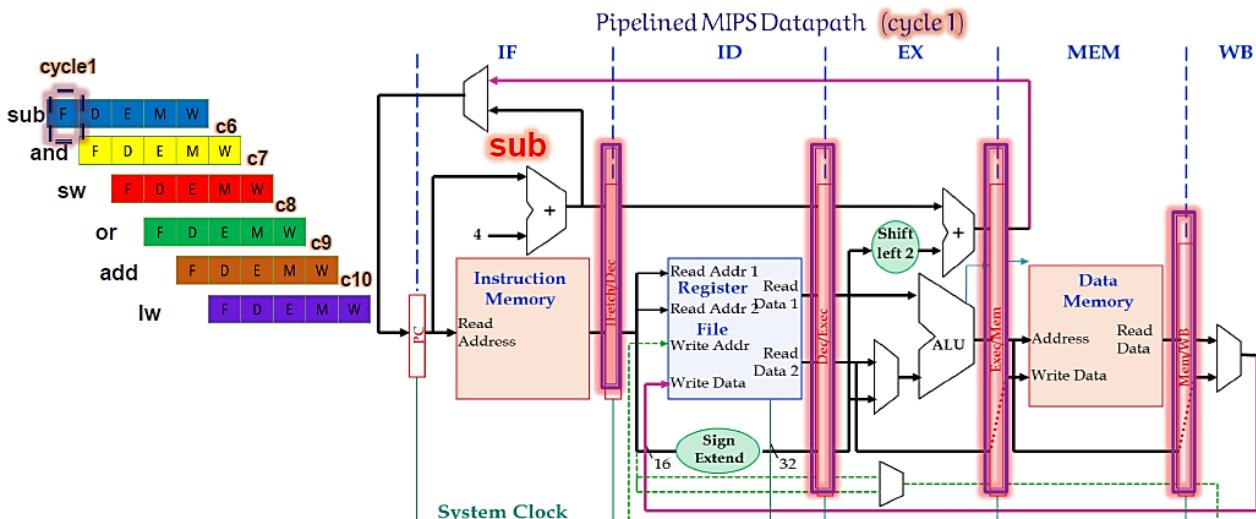

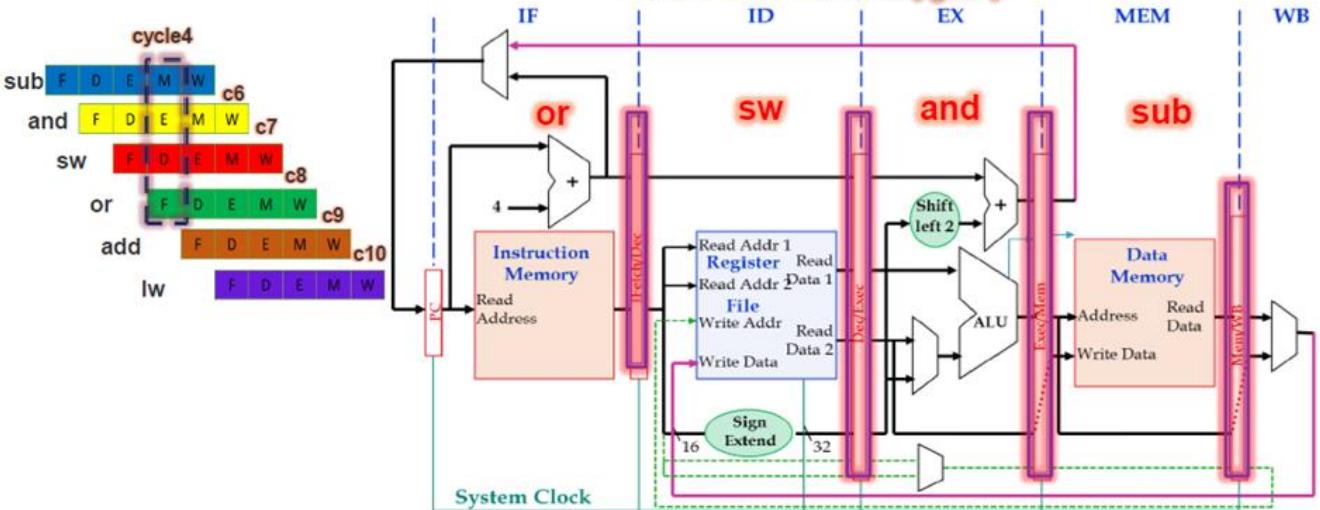

**تعريف 3** بفرض تم تنفيذ 6 تعليمات هي  $sub \rightarrow and \rightarrow sw \rightarrow or \rightarrow add \rightarrow lw$

على المعالج المتواارد التالي، وبفرض عدم وجود أية أعطال، حدد توزع التعليمات على المخطط المرفق في أول 5 أدوار من بدء التنفيذ، ثم حدد في أي دور ساعة يتم حفظ ناتج كل من التعليمتين  $or$  و  $lw$  في ملف السجلات؟

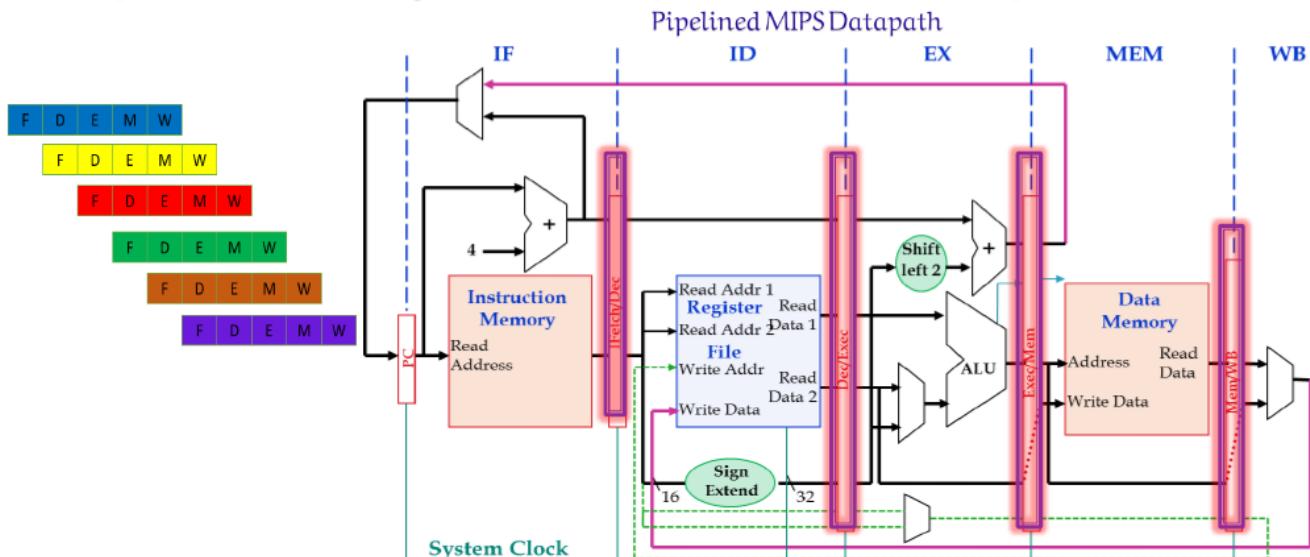

**ملاحظة** تم تقسيم عملية المعالجة إلى مراحل ( $F / D / E / M / W$ ) المرمزة فوق كل قسم في الرسمة، عند طلب توزع التعليمات في دور ما نبحث ضمن الدور عن المراحل التي تتم معالجتها في هذا الدور. وبما أن تنفيذ القيادة يتم على عدة أدوار لذا يلزم سجلات بينية بين المراحل لحفظ المعاملات والمعطيات وإشارات التحكم الخاصة بكل تعليمة مما تحتاجه المراحل التالية.

في الدور الأول تكون عملية  $sub$  في طور جلب التعليمة *IF*.

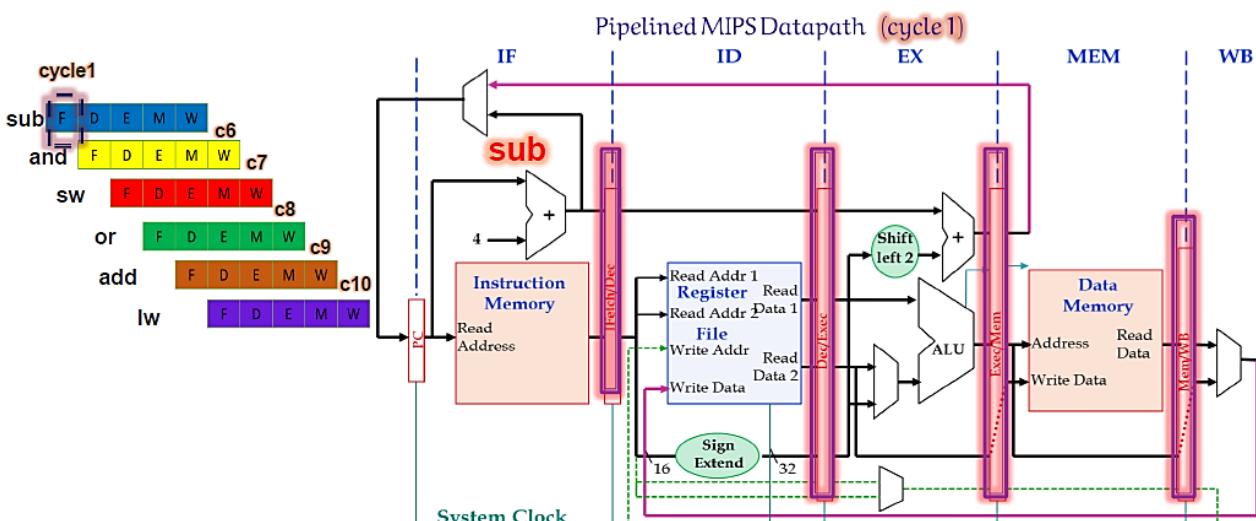

Pipelined MIPS Datapath (cycle2)

في الدور الثاني تنتقل عملية *sub* إلى مرحلة فك التشفير *ID* عن طريق السجل البيني *IF*، والواصل بين مرحلة جلب التعليمقة ومرحلة فك التشفير وفي ذات الوقت تبدأ عملية *and* في مرحلة *IF* جلب التعليمقة.

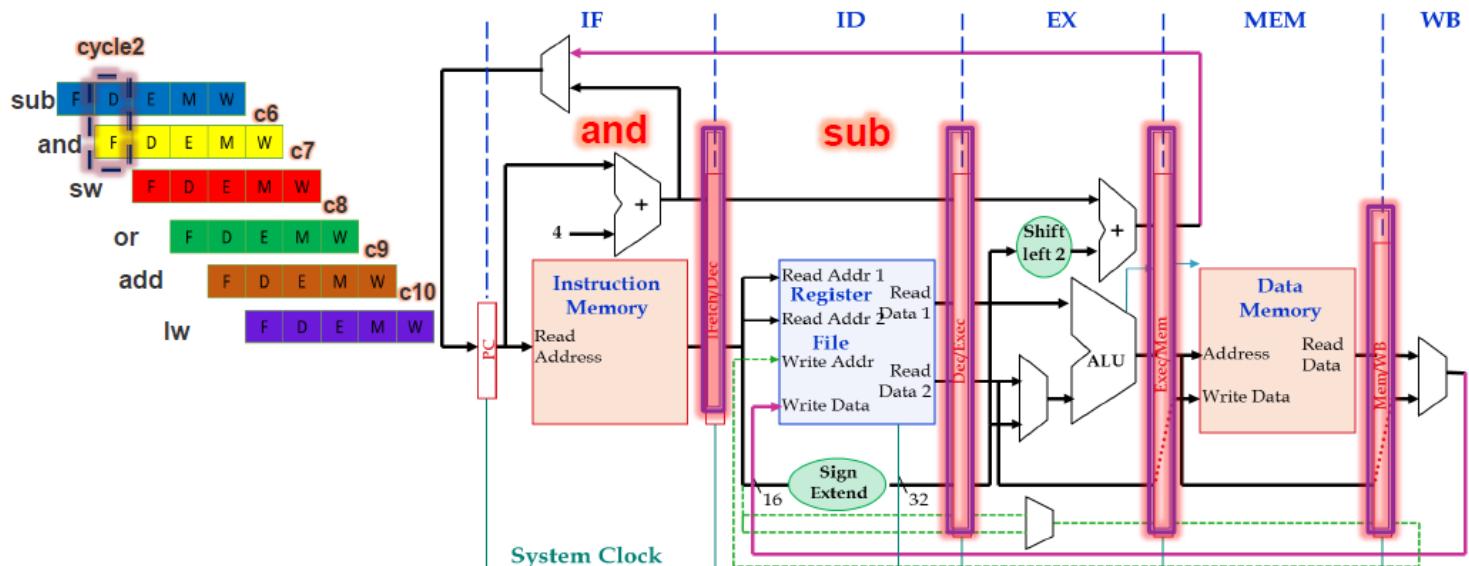

Pipelined MIPS Datapath (cycle3)

في الدور الثالث تنتقل عملية *sub* إلى مرحلة التنفيذ *EX* عن طريق السجل البيني *ID/EX* الوالصل بين مرحلة فك التشفير ومرحلة التنفيذ وفي نفس الوقت تنتقل عملية *and* إلى مرحلة فك التشفير وذلك عن طريق السجل البيني *IF/ID* الوالصل بين مرحلة جلب التعليمقة ومرحلة فك التشفير في حين أن عملية *sw* تبدأ بمرحلة الجلب *IF*.

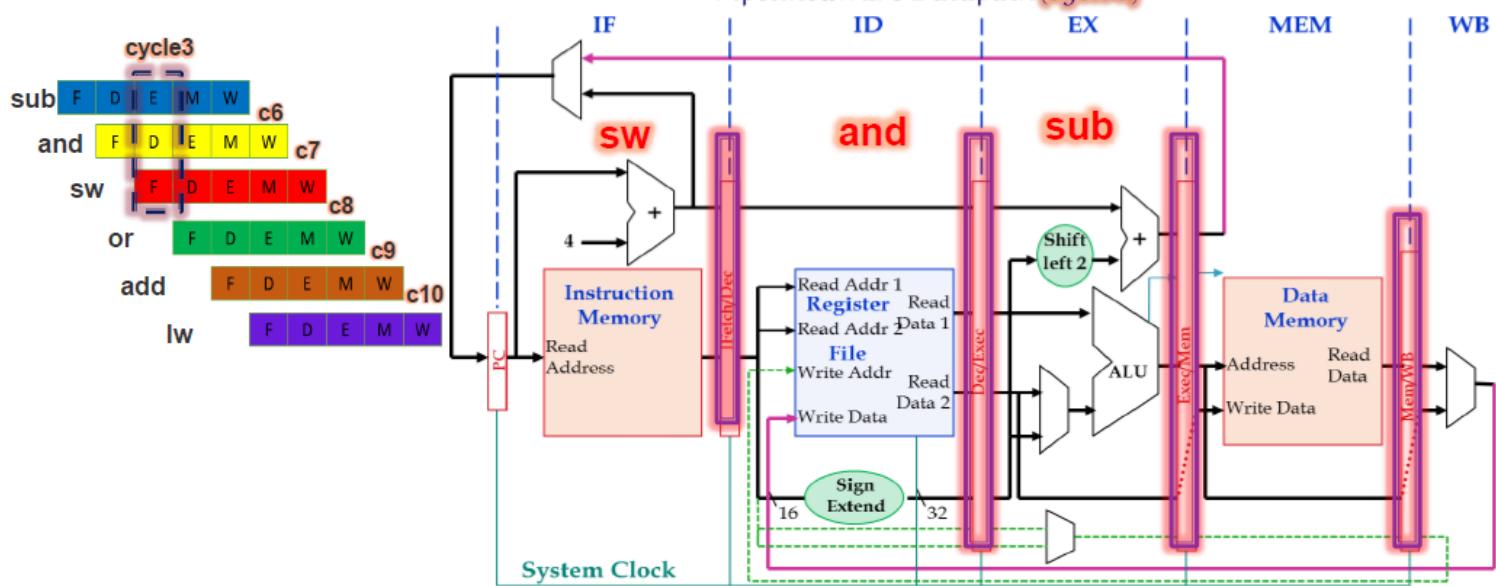

في الدور الرابع تنتقل عملية **sub** إلى مرحلة القراءة والكتابة على الذاكرة عن طريق السجل البيني **EX/MEM** الواصل بين مرحلة التنفيذ ومرحلة القراءة والكتابة على الذاكرة وفي نفس الوقت تنتقل عملية **and** إلى مرحلة التنفيذ **EX** عن طريق السجل البيني **ID/EX** الواصل بين مرحلة فك التشفير وممرحلة التنفيذ وفي ذات الوقت تنتقل عملية **sw** إلى مرحلة فك التشفير **ID** وذلك عن طريق السجل البيني **IF/ID** الواصل بين مرحلة جلب التعليمقة وممرحلة فك التشفير في حين أن عملية **sw** تبدأ بمرحلة الجلب **IF**.

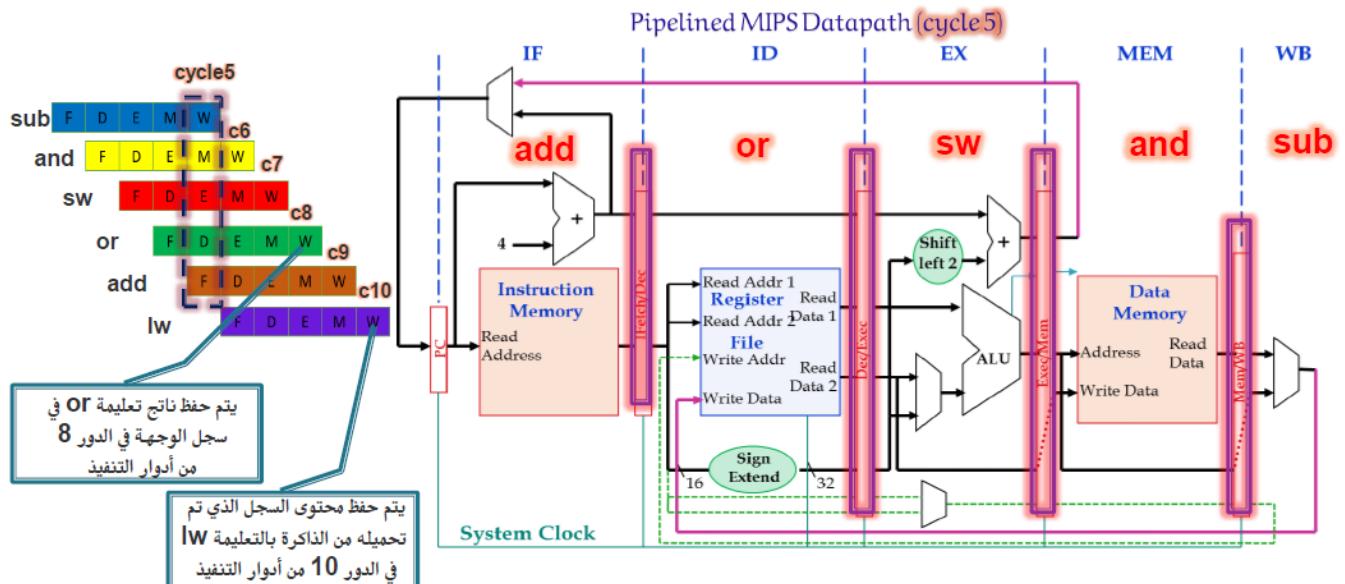

أما في الدور الخامس تنتقل عملية **sub** إلى طور العودة للكتابة على ملف السجلات **WB** (والذي من خلاله يتم حفظ نتيجة العملية بعد التنفيذ) بواسطة السجل البيني **MEM/WB** الواصل بين مرحلة القراءة والكتابة على الذاكرة ومرحلة العودة للكتابة. وفي أثناء ذلك تنتقل عملية **and** إلى مرحلة القراءة والكتابة على الذاكرة عن طريق السجل البيني **Mem** **EX/MEM** الواصل بين مرحلة التنفيذ ومرحلة القراءة والكتابة على الذاكرة وفي نفس الوقت تنتقل عملية **sw** إلى مرحلة التنفيذ **EX** عن طريق السجل البيني **ID/EX** الواصل بين مرحلة فك التشفير وممرحلة التنفيذ وفي ذات الوقت تنتقل

عملية ٥٢ إلى مرحلة فك التشفير *ID* وذلك عن طريق السجل البيني *IF/ID* الواصل بين مرحلة جلب التعليمية ومرحلة فك التشفير في حين أن عملية *add* تبدأ بمرحلة الجلب *IF*.

إجابة عن سؤال تحديد دور الساعة الذي يتم فيه حفظ ناتج كل من التعليمتين *or* و *lw* في ملف السجلات، نقوم بالبحث في الرسمة السابقة (رسم مخطط الدور الخامس) فنلاحظ أنه يتم حفظ ناتج تعليمية ٥٢ في سجل الوجهة في الدور 8 من أدوار التنفيذ. في حين أنه يتم حفظ محتوى السجل الذي تم تحميله من الذاكرة بالتعليمقة *lw* في الدور 10 من أدوار التنفيذ.

#### تعرين 4: (غير مطلوب في القسم العملي لكن يفيد في فهم الأفكار النظرية لبحث التوارد)

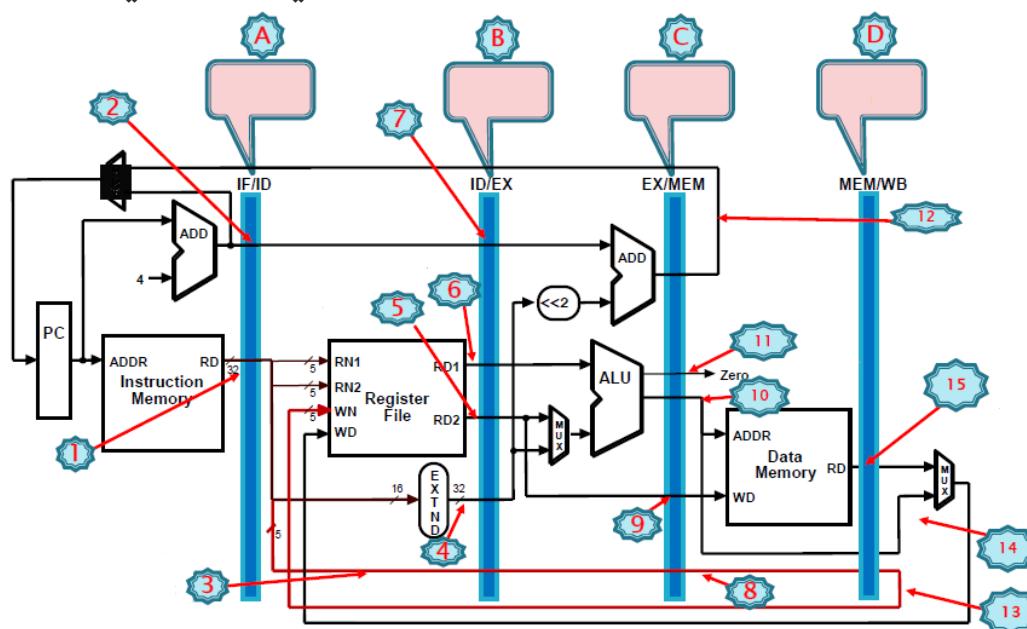

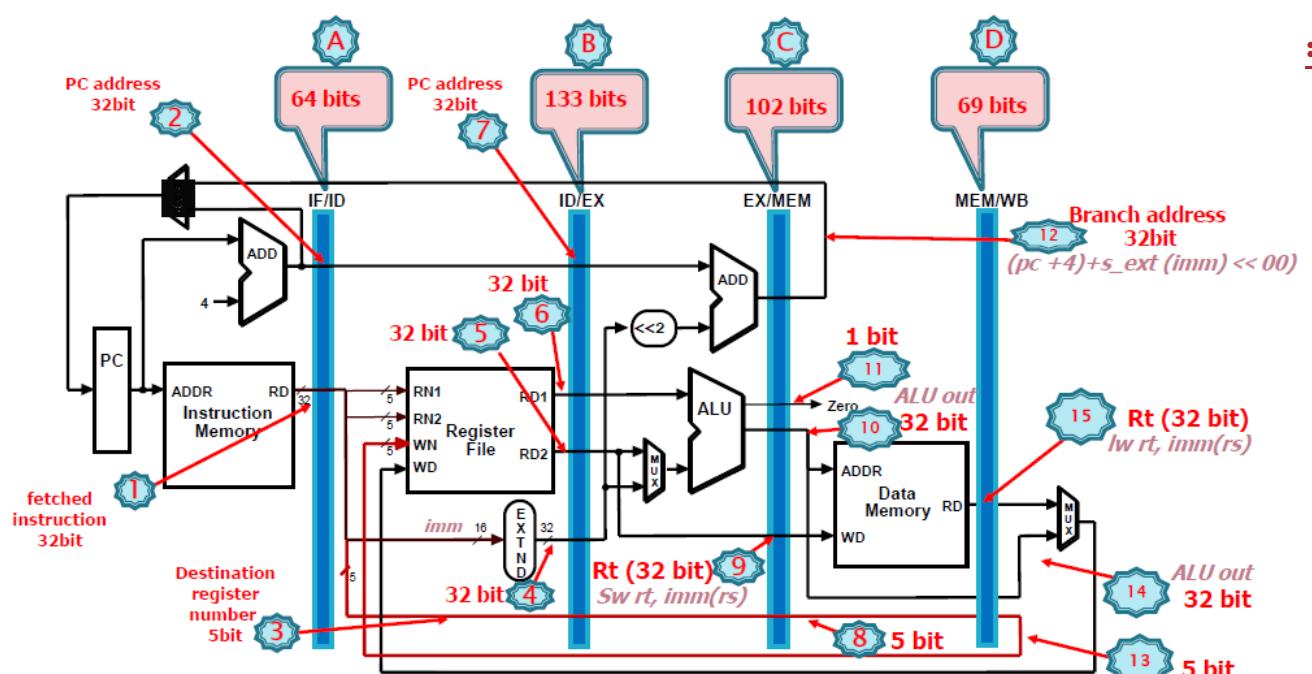

حدد عرض السجلات البيانية *IF/ID*, *ID/EX*, *EX/MEM*, *MEM/WB* في الشكل التالي:

▪

الحل:

### توضيح عملية الحل:

يدخل إلى السجل البياني  $IF/ID$  (الشكل A) مدخلين هما: الرقم 1 يمثل مسار التعليمية بعد الجلب والذي يخرج من المخرج  $RD$  من ذاكرة التعليمات ويبلغ حجمها 32 بت. أما الرقم 2 ف يمثل مسار عنوان عدد البرنامج  $PC$  بعد عملية الزيادة بمقدار  $(PC + 4)$  ويكون حجم محتوى هذا العنوان حوالي 32 بت. وبجمع القيم السابقة بالتالي يكون عرض السجل البياني  $IF/ID$  هو 64 بت.

يدخل إلى السجل البياني  $ID/EX$  (الشكل B) خمسة مدخلات هم: الرقم 3 يمثل مسار رقم سجل التعليمية العائدة بعد عملية الـ  $rd$  ويبلغ حجمها 5 بت. الرقم 4 يمثل مسار القيمة الفورية  $imm$  من ذاكرة التعليمات وذلك بعد اجراء عملية  $extend$  عليها عند تطبيق التعليمات من النوع  $Type - I$  – فيكون حجمها قبل العملية هو 16 بت أما بعد العملية (وهو الحجم المطلوب للسجل البياني) فيكون حجمها 32 بت. الرقم 5 يمثل مسار المخرج  $RD2$  من ملف السجلات والذي يحمل سجل المعطيات  $rt$  عند تطبيق التعليمات من النوع  $Type - I$  ويكون حجمه 32 بت. الرقم 6 يمثل مسار المخرج  $RD1$  من ملف السجلات والذي يحمل سجل المعطيات  $rs$  عند تطبيق التعليمات من النوع  $Type - R$  ويكون حجمه 32 بت. الرقم 7 يمثل مسار عنوان عدد البرنامج  $PC$  ويكون حجمه 32 بت. وبجمع القيم السابقة بالتالي يكون عرض السجل البياني  $ID/EX$  هو 133 بت.

يدخل إلى السجل البياني  $EX/MEM$  (الشكل C) خمسة مدخلات هم: الرقم 8 يمثل مسار رقم سجل التعليمية العائدة بعد عملية الـ  $WB$  (Write-Back) ويبلغ حجمها 5 بت. الرقم 9 يمثل مسار سجل المعطيات  $rs$  عند تطبيق تعليمة الـ  $sw$  وتكون واصلة إلى الذاكرة  $Mem$  ويكون حجمها 32 بت. الرقم 10 يمثل مسار المحتوى الناتج  $ALUout$  بعد عملية التنفيذ في الـ  $ALU$  ويكون حجمها 32 بت. أما الرقم 11 يمثل البت الصفرى  $zero$  وهو يتالف من بت وحيد يفيد في تعليمات التفرع الشرطي بحيث يعطي قيمة 1 عند وجود عملية تفرع بعد تحقق عملية المقارنة بين السجلات وقيمة 0 خلاف ذلك. الرقم 12 يمثل مسار عنوان عدد البرنامج  $PC$  بعد عملية التفرع بحيث يحسب عن طريق إضافة مقدار 4 للعنوان وجمعه مع القيمة الفورية  $imm$  بعد تطبيق عملية الـ  $extend$  بالإضافة إلى إزاحة الناتج بمقادير صفرتين نحو اليسار، يكون حجم محتوى عنوان البرنامج بعد تطبيق كل هذه العمليات هو 32 بت. وبجمع القيم السابقة نجد أن عرض السجل البياني  $EX/MEM$  هو 102 بت.

يدخل إلى السجل البياني  $MEM/WB$  (الشكل D) ثلاثة مدخلات هم: الرقم 13 يمثل مسار رقم سجل التعليمية  $rd$  العائدة بعد عملية الـ  $WB$  (Write – Back) ويبلغ حجمها 5 بت. الرقم 14 يمثل مسار المحتوى الناتج بعد عملية التنفيذ في الـ  $ALU$  ويكون حجمها 32 بت. الرقم 15 يمثل مسار المخرج  $RD$  من الذاكرة  $ALUout$  والتي يحمل محتوى السجل  $rs$  أثناء تطبيق عملية الـ  $lw$ . ويكون حجم محتوى هذا السجل هو 32 بت. عند جمع القيم السابقة نجد أن عرض السجل البياني  $MEM/WB$  هو 69 بت.

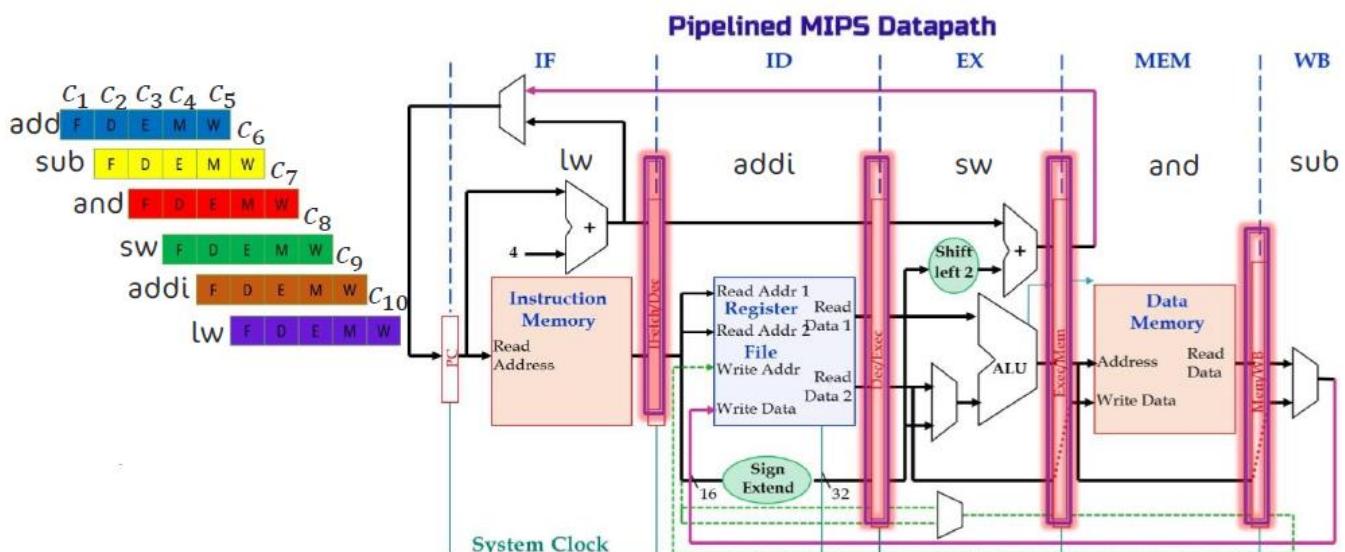

**وظيفة 1:** بفرض تم تنفيذ 6 تعليمات هي  $add \rightarrow sub \rightarrow and \rightarrow sw \rightarrow addi \rightarrow lw$  على المعالج المتواارد التالي، وبفرض عدم وجود أية أعطال، حدد توزيع التعليمات على المخطط المرفق في الدور السادس من بدء التنفيذ، ثم حدد في أي ساعة يتم حفظ ناتج التعليمات المرفقة في ملف السجلات؟

الحل:

بنفس طريقة حل التمرين الثالث ولتحديد دور الساعة الذي يتم فيه حفظ ناتج التعليمات في ملف السجلات، نقوم بالبحث في رسم مخطط الدور السادس (وذلك بعد توزيع كل التعليمات على المعالج المتواارد) عن المرحلة w في التعليمات المطلوبة فنلاحظ أنه سيتم حفظ التعليمات sub في الدور السادس والتعليمات addi في الدور التاسع والتعليمات lw في الدور العاشر.

## الأعطال Hazards

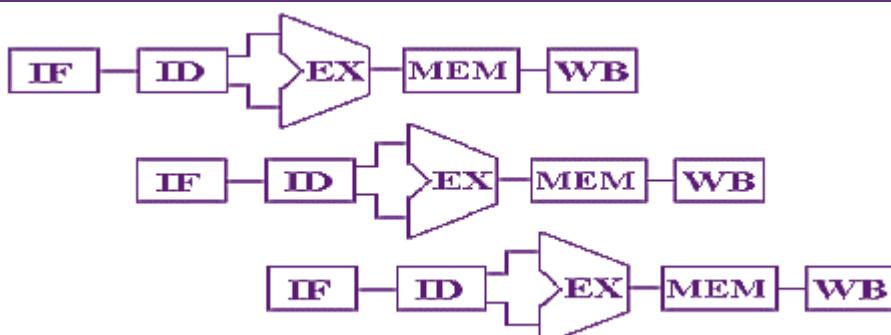

مراحل معالج MIPS المتوازدة الخامسة:

1. جلب التعليمية Fetch

2. فك تشفير التعليمية Decode

3. التنفيذ في وحدة الحساب والمنطق Execution

4. القراءة والكتابة على الذاكرة Memory

5. العودة للكتابة على ملف السجلات Write-Back

### أنواع الأعطال

#### 1. الأعطال البنوية Structural Hazards

تحدث نتيجة التنازع على نفس الموارد في المعالج (مثل وجود ذاكرة وحيدة، أو ALU وحيدة.. الخ)، مثل تعليمية تقوم بعملية جلب تعليمية من الذاكرة وتتعليمية أخرى تقوم بالتخزين على الذاكرة في نفس الدور حيث لا يمكن استخدام نفس المورد في الوقت ذاته لتعليمتين مختلفتين. ولحل العطل البنوي نلجأ إلى الانتظار حتى الانتهاء من استخدام المورد أو نلجأ إلى شراء مورد جديد.

**ملاحظة** سنفترض في مسائل العملي أن الأعطال البنوية محلولة بتوفير الموارد اللازمة، مثلً يمكن حل مشكلة التنازع على الذاكرة بتوفير خبيتين للتعليمات وللمعطيات ...  $D_Cache, I_Cache$

#### 2. أعطال المعطيات Data Hazards

ناتجة عن ترابط المعطيات أي عندما تحتاج تعليمية لمعطيات ناتجة عن تعليمية سابقة لا تزال موجودة في قناة التوارد PC (مثل طلب قراءة قيمة سجل تم التعديل عليه بتعليمية سابقة قبل تحديد القيمة).

#### 3. أعطال التحكم Control Hazards

ناتجة عن تعليمات القفز والتفرع (j, beq, bne, ...).

**ملاحظة** سنتناول في هذه المحاضرة فقط أعطال المعطيات باعتبار أن الأعطال البنوية محلولة سابقا، أما أعطال التحكم ف سنبدأ بها في المحاضرة القادمة.

“Everything you can imagine is real.”

—Pablo Picasso

## أعطال المعطيات Data Hazards

▪ تحدث عندما تحتاج تعليمة لمعطيات ناتجة عن تعليمة سابقة لا تزال موجودة في قناة التوارد  $PL$ .

▪ الحلول الممكنة:

▪ التأخير الزمني Stalls / إضافة فقاعات Bubbles (حل عتادي يحتاج إضافة دارة كشف الأعطال *(Hazard Detection Unit)*).

▪ إضافة دارة إحالة *Bypassing / Forwarding Unit* للحصول على المعطيات دون انتظار الكتابة *Writing*.

▪ إضافة دارة كشف الأعطال *Hazard Detection Unit* على الوجهة (حل عتادي يحتاج أيضاً إضافة دارة كشف الأعطال *Hazard Detection Unit*).

▪ إعادة ترتيب البرنامج عن طريق المترجم *Compiler* بحيث يتم المباعدة بين التعليمات المتراكبة.

▪ وإضافة NOP عند الحاجة (حل برمجي).

**ملاحظة:** يتم تمثيل NOP في لغة تجميع MIPS على الشكل التالي:

In MIPS:  $NOP = \text{"no operation"} = 00 \dots 0$  (32bits) =  $sll \$0, \$0, 0 \#SLL: shift left logical$

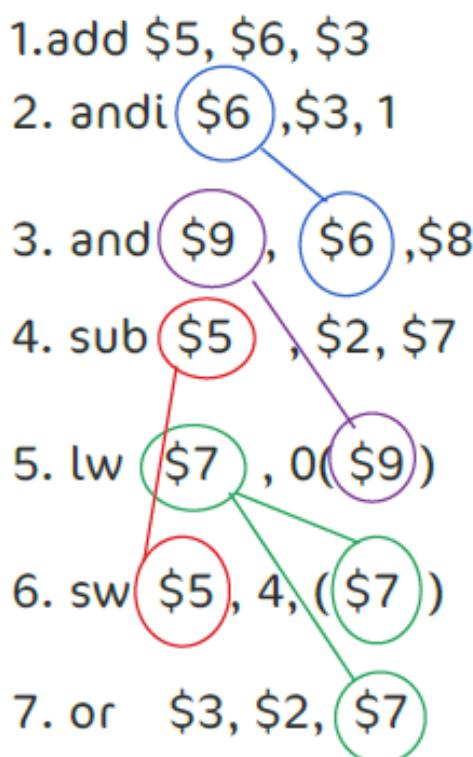

▪ **تعريف 5:** لدينا البرنامج التالي ينفذ على معالج MIPS متوارد، حدد ترابطات المعطيات الموجودة في البرنامج، ثم مثل أدوار التنفيذ باستخدام طريقة التأخير الزمني Stall (إضافة فقاعات Bubble) لمعالجة أعطال المعطيات بفرض عدم وجود أعطال بنوية، وبفرض إمكانية النفاذ المزدوج لملف السجلات (إمكانية الكتابة والقراءة بنفس الدور).

- 1.  $sub \$5, \$6, \$3$

- 2.  $andi \$6, \$3, 1$

- 3.  $and \$9, \$6, \$8$

- 4.  $add \$5, \$2, \$7$

- 5.  $lw \$7, 0(\$9)$

- 6.  $sw \$5, 4(\$7)$

- 7.  $or \$3, \$2, \$7$

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

نحدد الترابطات بين أسطر التعليمات عن طريق البحث عن أي تعليمة تقوم بقراءة سجل بعد تعليمة قامت بالكتابة على نفس السجل (read after write RAW). فنلاحظ أنه في أول تعليمة لا يوجد قبلها كتابة على أي سجل فلا يوجد ترابط. في التعليمة الثالثة نلاحظ وجود ترابط بينها وبين سابقتها حيث في التعليمة الثانية يتم الكتابة على السجل \$6 وبنفس الوقت تتم قراءة قيمة السجل في التعليمة الثالثة مما قد يؤدي لحدوث أخطاء لدى عملية القراءة.

يوجد أيضاً الترابط بين التعليمتين السادسة والرابعة حيث تتم عملية القراءة من محتوى السجل \$5 في التعليمة السادسة أثناء انتهاء تنفيذ عملية الكتابة على نفس السجل في التعليمة الرابعة. كما يوجد ترابط بين التعليمتين الخامسة والثالثة حيث تتم عملية القراءة من محتوى السجل \$9 في الذاكرة من العنوان 0 في التعليمة الخامسة أثناء انتهاء تنفيذ الكتابة على نفس السجل في التعليمة الثالثة. كما يوجد ترابط بين التعليمات الخامسة والسادسة والسابعة حيث تتم عملية القراءة من محتوى السجل \$7 في الذاكرة من العنوان 4 في التعليمة السادسة أثناء انتهاء تنفيذ الكتابة على نفس السجل في التعليمة الخامسة. وتتم عملية القراءة من السجل \$7 من أجل تنفيذ العملية المنطقية  $0_2$  في التعليمة السابعة أثناء انتهاء تنفيذ الكتابة على نفس السجل في التعليمة الخامسة.

**ملاحظة** لم نأخذ ترابط بين التعليمة السادسة والتعليق الأولى (على الرغم من وجود عملية قراءة ل\$5 في السادسة وعملية كتابة على \$5 في الأولى) والسبب هو أنها بحث عن آخر تعديل على قيمة السجل ولا نهتم للتعديلات السابقة لقيمة \$5 تعدلت في التعليقات الأولى والرابعة وقيمتهما التي تهمنا بعد آخر تعديل فالترابط يكون مع آخر تعديل على السجل فقط.

### كيفية تعبئة الجدول

عند تعبئة الجدول في حال وجود ترابط بين التعليمات المراد تعيينها مع تعليمات سابقة ننظر إلى المرحلة D في تعليمتنا وإلى المرحلة في التعليمية المترابطة معها ونناقش الحالات الثلاثة التالية:

1. تمت عملية W في دور قبل الدور الذي يمكن وضع D فيه: نضع D ونكمel بشكل طبيعي.

2. تتم عملية W في نفس الدور الذي يمكن وضع D فيه: في حال النفاذ المزدوج نضع D بشكل طبيعي وفي حال عدم وجود نفاذ نضع فقاعة ثم D.

3. تتم عملية W في دور بعد الدور الذي يمكن وضع D فيه: ترك فقاعات إلى أن نصل إلى الدور W ونضع D بحيث تكون W مباشرة بذلك في حال النفاذ المزدوج وفي حال عدم وجوده ترك فقاعة زيادة.

فيصبح الجدول على الشكل التالي

| 1 | 2 | 3                                                                                   | 4                                                                                   | 5 | 6 | 7                                                                                   | 8                                                                                   | 9                                                                                    | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|---|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---|---|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----|----|----|----|----|----|----|

| F | D | E                                                                                   | M                                                                                   | W |   |                                                                                     |                                                                                     |                                                                                      |    |    |    |    |    |    |    |

| F | D | E                                                                                   | M                                                                                   | W |   |                                                                                     |                                                                                     |                                                                                      |    |    |    |    |    |    |    |

|   | F |  |  | D | E | M                                                                                   | W                                                                                   |                                                                                      |    |    |    |    |    |    |    |

|   |   |                                                                                     |                                                                                     | F | D | E                                                                                   | M                                                                                   | W                                                                                    |    |    |    |    |    |    |    |

|   |   |                                                                                     |                                                                                     |   | F |  | D                                                                                   | E                                                                                    | M  | W  |    |    |    |    |    |

|   |   |                                                                                     |                                                                                     |   |   | F                                                                                   |  |  | D  | E  | M  | W  |    |    |    |

|   |   |                                                                                     |                                                                                     |   |   |                                                                                     |                                                                                     |                                                                                      | F  | D  | E  | M  | W  |    |    |

$$CPI = \frac{5 + (IC - 1) + stalls}{IC} = \frac{5 + 6 + 5}{7} = \frac{16}{7} = 2.3$$

**ملاحظة** بها أن التعريرين ينص على إمكانية النفاذ المزدوج إلى ملف السجلات أمكننا وضع المرحلة D في الدور السادس مع المرحلة W على نفس السجل وفي نفس الدور وإذا لم ينص التعريرين على النفاذ المزدوج يجب وضع فقاعة ثلاثة والانتظار للانتهاء من W ووضع D في الدور السابع .

## 2. أعد الحل بفرض أن قراءة السجلات تتم في المرحلة E

بنفس الطريقة السابقة تماما ولكن من أجل المرحلة E نجد أن:

1. sub \$5,\$6,\$3

2. andi \$6, \$3 , 1

3. and \$9, \$6, \$8

4. add \$5 , \$2 , \$7

5. lw (\$7 ,0(\$9

6. sw \$5 , 4 (\$7)

7. or \$3 , \$2 , \$7

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |

| F | D |   |   | E | M | W |   |   |    |    |    |    |    |    |    |    |

| F |   |   | E | M | W |   |   |   |    |    |    |    |    |    |    |    |

| F |   |   |   | E | M | W |   |   |    |    |    |    |    |    |    |    |

| F |   |   |   |   | E | M | W |   |    |    |    |    |    |    |    |    |

| F |   |   |   |   |   | E | M | W |    |    |    |    |    |    |    |    |

**ملاحظة:**

لا يمكن هنا إجراء

W و E على نفس

السجل في نفس الدور

لأن خاصية النفاذ

المزدوج تنص على

إمكانية الكتابة على

ملف السجلات في

نصف الدور ثم

القراءة منه في نصف

الدور، ولا تنص على

إمكانية إجراء E في

نصف الدور!

$$CPI = \frac{\{5+(IC-1)+stalls\}}{IC} = \frac{\{5+6+5\}}{7} = \frac{16}{7} = 2.3$$

تمرين 6: (للتدريب): بفرض لدينا البرنامج التالي ينفذ على معالج MIPS متواحد، حدد ترابطات المعطيات الموجودة في البرنامج، ثم مثل أدوار التنفيذ بفرض استخدام طريقة التأخير الزمني Stall (إضافة فقاعات Bubble) لمعالجة أخطاء المعطيات بفرض عدم وجود أخطاء بنوية، وبفرض إمكانية النفاذ المزدوج لملف السجلات (إمكانية الكتابة والقراءة بنفس الدور).

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

1. and \$8 , \$9, \$4

2. ori \$5 , \$3 , 5

3. add \$6, \$4, \$8

4. or \$2 , \$6 , \$7

5. lw \$9, 0( \$3 )

6. sw \$4 , 4 ( \$2 )

7. sub \$5 , \$4 , \$3

1. بفرض أن قراءة السجلات تتم في المرحلة D

1. and \$8,\$9,\$4

2. ori \$5 , \$3 , 5

3. add \$6, \$4, \$8

4. or \$2 , \$6, \$7

5. lw \$9 , 0(\$3 )

6. sw \$4 , 4(\$2 )

7. sub \$5 , \$4 , \$3

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   | F | D | E | M | W |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   | F  | D  | E  | M  | W  |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   | F  | D  | E  | M  | W  |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

$$CPI = \frac{\{5+(IC-1)+stalls\}}{IC} = \frac{\{5+6+4\}}{7} = \frac{15}{7} = 2.14$$

2. أعد حل التمرين السابق بفرض أن قراءة السجلات تتم في المرحلة E

1. and \$8,\$9,\$4

2. ori \$5 , \$3 , 5

3. add \$6, \$4, \$8

4. or \$2 , \$6, \$7

5. lw \$9 , 0(\$3 )

6. sw \$4 , 4(\$2 )

7. sub \$5 , \$4 , \$3

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

| F | D | E | M | W |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   | F | D | E | M | W |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   | F  | D  | E  | M  | W  |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   | F  | D  | E  | M  | W  |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |

$$CPI = \frac{\{5+(IC-1)+stalls\}}{IC} = \frac{\{5+6+4\}}{7} = \frac{15}{7} = 2.14$$

“Don’t limit your challenges. Challenge your limits.”

**وظيفة 2 (للتدريب):** حدد ترابطات المعطيات ثم مثل أدوار تنفيذ البرنامج التالي على المعالج المتواجد بخمس مراحل، واحسب CPI (بفرض عدم وجود أعطال بنوية وعدم وجود دارة إهالة) وبفرض أن قراءة السجلات تتم في المرحلة ٤.

1. add \$5,\$3,\$2

2. sub \$8, \$3, \$5

3. andi \$3, \$8, 2

4. or \$4 , \$8 , \$1

5. lw \$2 ,0 (\$3 )

6. and \$5, \$4, \$2

7. sw \$2 , 4 (\$11)

الحل:

- ```

graph TD

N1["1. add $5, $3, $2"] --> N2["2. sub $8, $3, $5"]

N2 --> N3["3. and $3, $8, 2"]

N3 --> N4["4. or $4, $8, $1"]

N4 --> N5["5. lw $2, 0($3)"]

N5 --> N6["6. and $5, $4, ($2)"]

N6 --> N7["7. sw $2, 4, ($11)"]

```

$$C = 5 + (7 - 1) + 7 = 5 + 6 + 7 = 18$$

$$CPI = \frac{CC}{IC} = \frac{18}{7} \approx 2.57$$

وبالتالي نجد أنه يوجد حوالي 7 ترابطات بالإضافة إلى 7 أدوار تأخير stalls و تكون قيمة CPI هي  $CPI = 18/7 = 2.57$

انتهت المحاضرة