2/11/2022

## تصميم وحدة التحكم Control Unit (2)

م. عبير ميا م. مصعب خبار

محتوى مجاني غير مخصص للبيع التجاري

## بنية الحاسوب 2

### تمكناً حل السؤال من المحاضرة السابقة

اكتب مراحل تنفيذ التعليمات التسعة السابقة بلغة نقل السجلات (RTL (Register Transfer Language))

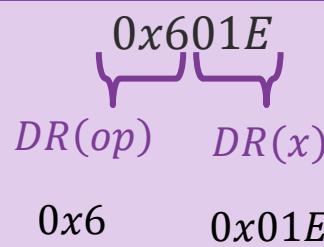

$$\begin{aligned} F_1: AR &\leftarrow PC \\ F_2: DR &\leftarrow M[AR]; PC \leftarrow PC + 1 \\ F_3: IR &\leftarrow DR(op); AR \leftarrow DR(x) \end{aligned}$$

}

والآن بعد أن تعرفنا على مرحلة جلب

التعليمية *fetch* والتي تمر بثلاث مراحل

- 1.  $MOV_R \Leftrightarrow R \leftarrow AC$

- 2.  $SUB_R \Leftrightarrow AC \leftarrow AC - R$

- 3.  $OR_R \Leftrightarrow AC \leftarrow AC \text{ or } R$

- 4.  $LDR_D x \Leftrightarrow R \leftarrow M[x]$

- 5.  $STAC_D x \Leftrightarrow M[x] \leftarrow AC$

- 6.  $STR_ID x \Leftrightarrow M[M[x]] \leftarrow R$

- 7.  $SUB_D x \Leftrightarrow AC \leftarrow AC - M[x]$

- 8.  $JMP_D x \Leftrightarrow \text{Jump to direct address}$

- 9.  $NOP \Leftrightarrow \text{No Operation (Do Nothing)}$

▪ وعلمنا بأن جميع التعليمات تمر بهذه المراحل

الثلاث لجلبها من الذاكرة.

▪ الآن سنقوم بمعرفة عدد مراحل كل تعليمية من

التعليمات التسعة السابقة ونقصد هنا بعدد

مراحل التعليمية أي عدد تعليمات *fetch*

بالإضافة إلى عدد مراحل تنفيذ هذه التعليمية.

$$\text{عدد مراحل التنفيذ} = 3 + \text{عدد مراحل التنفيذ}$$

### تذكرة

- أي عنوان ذاكرة يجب التعامل معه عن طريق *AR*.

- أي قيمة تقوم بجلبها من الذاكرة أو كتابتها بالذاكرة (*data*) يجب أن تمر على *DR*.

$MOV_R: R \leftarrow AC$

.1

في هذه التعليمية سنقوم فقط بنقل محتوى المراكم  $AC$  إلى السجل  $R$  أي ستنفذ في مرحلة واحدة بالإضافة إلى 3 مراحل  $fetch$  (فتكون عدد مراحل التعليمية  $MOV_R = 4$  مراحل)

$SUB_R: AC \leftarrow AC - R$

.2

بالبداية سيكون عدد مراحل هذه التعليمية 3 وهي عدد مراحل  $fetch$  ولكن نلاحظ بأن هذه المراحل غير كافية لأن التعليمية لم تتنفذ بعد فمرحلة التنفيذ تتلخص بطرح محتوى السجل  $R$  من المراكم  $AC$  ووضعها في  $AC$  (فتكون عدد مراحل تعليمية  $SUB_R = 4$  مراحل).

$OR_R: AC \leftarrow AC \text{ or } R$

.3

كما فعلنا في التعليمية السابقة سنجد أن مراحل هذه التعليمية هي 4 أيضاً.

ملاحظة: في التعليمات السابقة لم نستخدم  $AR$  أو  $DR$  لأن التعديلات ستكون على السجلات فقط لم نضطر للوصول للذاكرة بالإضافة إلى أن مرحلة تنفيذ التعليمية كانت على مرحلة واحدة.

$LDR_D x: R \leftarrow M[x]$

.4

بالإضافة إلى مراحل  $fetch$  ستكون مراحل تنفيذ التعليمية على الشكل:

$$LDR_{D_1}: DR \leftarrow M[AR]$$

$$LDR_{D_2}: R \leftarrow DR$$

هنا قمنا باستبدال  $x$  (عنوان الذاكرة) بـ  $AR$  لماذا؟؟ (لأن أي عنوان ذاكرة نتعامل معه عن طريق  $AR$ ) ومن ثم وضعنا محتوى عنوان الذاكرة (**data**) في  $DR$  (أي قيمة نقوم بجلبها أو وضعها في الذاكرة يكون عن طريق  $DR$ ) ومن ثم نضع محتوى  $DR$  في السجل  $R$  لإكمال تنفيذ التعليمية.

الآن نجد بأنه لدينا مراحلتين تنفيذ بالإضافة إلى مراحل  $fetch$   $\Leftarrow$  عدد مراحل تعليمية  $LDR_D = 5 = 5$  مراحل.

$STAC_D x: M[x] \leftarrow AC$

.5

مراحل التنفيذ على الشكل:

$STAC_{D_1}: DR \leftarrow AC$

$STAC_{D_2}: M[AR] \leftarrow DR$

بداية قمنا بنقل محتوى  $AC$  لـ  $DR$  لأنها معطيات ونريد وضعها في عنوان في الذاكرة ومن ثم قمنا بنقل محتوى  $DR$  لعنوان الذاكرة.

(وبالتالي تكون عدد مراحل التعليمية  $STAC_D$  هي 5 مراحل)

*STR\_ID x: M[M[x]] ← R*

.6

*STR\_ID<sub>1</sub>: DR ← M[AR]*

*STR\_ID<sub>2</sub>: AR ← DR*

*STR\_ID<sub>3</sub>: DR ← R*

*STR\_ID<sub>4</sub>: M[AR] ← DR*

هنا نجد بأن العنونة غير مباشرة هذا يعني بأن محتوى *M[x]* هو أيضاً عنوان ذاكرة بداخله أي *M[M[x]]* المحتوى الذي نريد استبداله بمحتوى السجل *R*.

■ **شرح الخطوات:** بداية قمنا بوضع محتوى عنوان الذاكرة في *DR* ومن ثم قمنا بوضع محتوى *AR* بالـ *DR* (وذلك لأن *DR* حالياً يحتوي على عنوان ذاكرة) ثم نقوم بوضع محتوى السجل *R* بالـ *DR* لأنها معطيات ونريد وضعها في عنوان ذاكرة ثم نقوم بوضع *DR* في عنوان الذاكرة المطلوب وبالتالي عدد مراحل التعليمية هي 7.

*SUB\_D x: AC ← AC – M[x]*

.7

تكون مراحل التنفيذ بالشكل:

*SUB\_D<sub>1</sub>: DR ← M[AR]*

*SUB\_D<sub>2</sub>: AC ← AC – DR*

نقوم بوضع محتوى عنوان الذاكرة *M[AR]* في *DR* (قيمة قمنا بجلبها من الذاكرة) ومن ثم قمنا بطرح محتوى *DR* من المراكم *AC* ومن ثم وضع الناتج في *AC*.

ف تكون عدد مراحل هذه التعليمية هي 5 مراحل.

*JMP\_D x: Jump to direct address*

.8

*JMP\_D<sub>1</sub>: DR ← M[AR]*

*JMP\_D<sub>2</sub>: PC ← DR(x)* هنا العنونة مباشرة أي *M[x]* ف تكون مراحل التنفيذ بالشكل:

قمنا بوضع محتوى عنوان الذاكرة *M[AR]* في *DR* ومن ثم نقلنا محتوى *DR* للـ *PC* ف تكون عدد المراحل تساوي 5 مراحل.

تختلف تعليمة *JMP* بحسب نوع العنونة في التعليمية السابقة كانت العنونة مباشرة أما في حال كانت العنونة فورية فسيكون عدد المراحل يساوي 4 مراحل.

*JMP 64: PC ← 64*

ستكون مراحل التعليمية هي تعليمة التنفيذ (وضع الثابت 64 في *PC*) بالإضافة إلى تعليمات *fetch* ← 4 مراحل

*JMP: PC ← DR(x)*

أما في حال كانت العنونة غير مباشرة  $x$  أي  $JMP ID$

$JMP\_ID_1: DR \leftarrow M[AR]$

$JMP\_ID_2: AR \leftarrow DR$

$JMP\_ID_3: DR \leftarrow M[AR]$

$JMP\_ID_4: PC \leftarrow DR$

وبالتالي سيكون عدد المراحل هو 7 مراحل.

### NOP: No Operation (Do Nothing)

.9

أيضاً مراحل هذه التعليمية ستكون 4 وذلك لأنه أول 3 مراحل هي *fetch* لجلب التعليمية من الذاكرة والمراحل التالية ستكون لتحليل التعليمية وتنفيذها وحفظ النواتج وبالتالي احتجنا هنا لمرحلة رابعة لتحليل التعليمية حتى لو لم تكن تقوم بأي شيء كتنفيذ *Decode*.

3. بفرض كانت القيم الابتدائية للسجل  $PC = 0x01B$  وكان محتوى الكلمة الذاكرة ذات العنوان  $0x01B$  هو  $601E$  ما هي قيم السجلات  $PC, AR, DR, IR$  خلال كل مرحلة من مراحل جلب وتنفيذ التعليمية  $LDR_D 0x01E$ ؟

| Address | 018  | 019  | 01A  | 01B  | 01C  | 01D  | 01E  | 01F  |

|---------|------|------|------|------|------|------|------|------|

| Content | 901E | 001F | 01B5 | 601E | 1D05 | 0020 | 3020 | 2011 |

| state                                                                                                                      | PC                  | AR    | IR  | DR     | R      |

|----------------------------------------------------------------------------------------------------------------------------|---------------------|-------|-----|--------|--------|

| $F_1: AR \leftarrow PC$<br>نسخ محتوى PC للسجل                                                                              | 0x01B               | 0x01B | —   | —      | —      |

| $F_2: DR \leftarrow M[AR];$<br>نقل محتوى العنوان AR للسجل<br>$DR$<br>$PC \leftarrow PC + 1$<br>زيادة محتوى العداد بمقدار 1 | $0x01B + 1 = 0x01C$ | 0x01B | —   | 0x601E | —      |

| $F_3: IR \leftarrow DR(op);$<br>$AR \leftarrow DR(x)$                                                                      | 0x01C               | 0x01E | 0x6 | 0x601E | —      |

| $LDR D_1: DR \leftarrow M[AR]$<br>وضع محتوى العنوان الموجود بالذاكرة(من جدول الذاكرة) بالسجل DR.                           | 0x01C               | 0x01E | 0x6 | 0x3020 | —      |

| $LDR D_2: R \leftarrow DR$<br>نسخ محتوى السجل DR ووضعه في السجل R.                                                         | 0x01C               | 0x01E | 0x6 | 0x3020 | 0x3020 |

عندما نجد  $M[AR]$  لا ننظر لمحتوى السجل  $AR$  في الجدول نقوم بالنظر في جدول الذاكرة على محتوى العنوان  $AR$ .

مثال:

| في الجدول   | في الذاكرة  |

|-------------|-------------|

| $AR: 0x01E$ | $01E: 3020$ |

$DR \leftarrow M[AR]$  ولدينا التعليمة

$DR: 0x3020$   $DR$  فتصبح

وغالباً ما نتعامل مع  $AR$  فقط كعنوان ذاكرة وبداخله محتوى أي بالشكل  $M[AR]$  ونتعامل معه كسجل كما في التعليمة  $.AR \leftarrow DR$  أو  $AR \leftarrow PC$ .

لا ننسى بأننا نتعامل بالنظام السادساني عشر وبالتالي علينا أن نراعي ذلك في العمليات كالجمع والطرح وغيرها.

في الجدول السطور الثلاثة الأولى نكتبها دائماً وهي عبارة عن تعليمات  $fetch$  والتي تمر بها كل تعليمة أما بعدها فتختلف التعليمة حسب المطلوب بالسؤال.

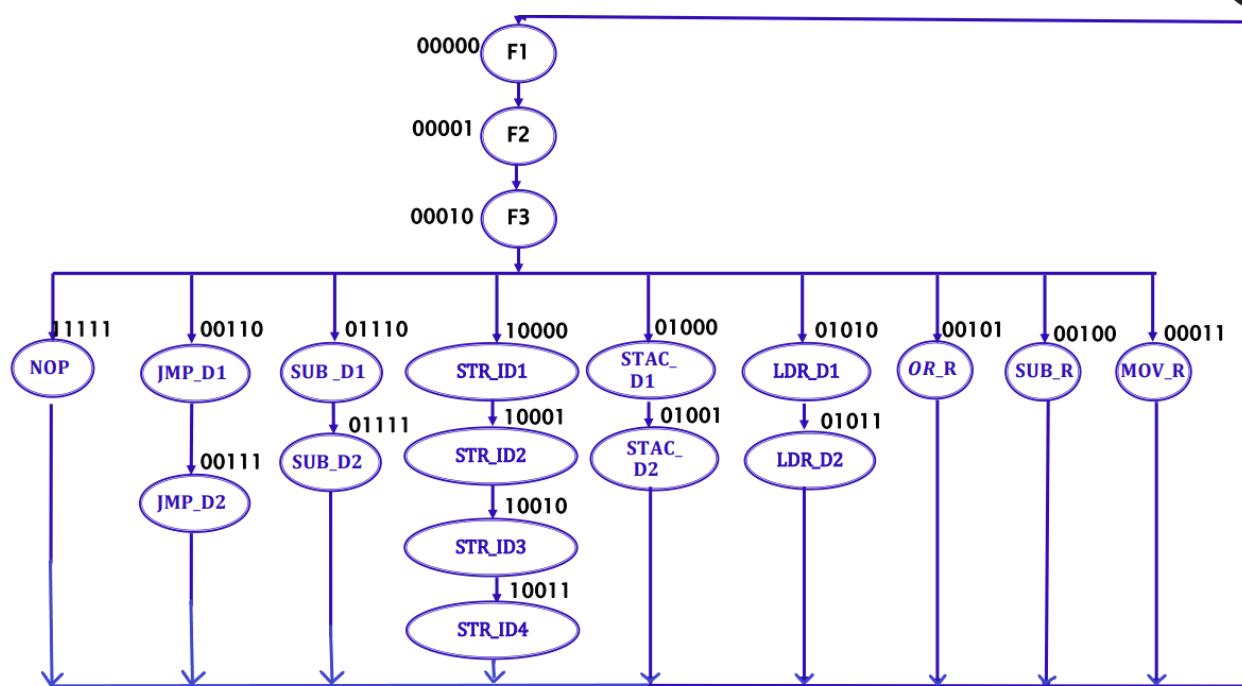

#### 4. ارسم مخطط الحالات مع ترميز الحالات.

بداية عدد الحالات = عدد الترميزات  $fetch$  (أي 3) + عدد مراحل التنفيذ فقط لكل تعليمة (16)

$$(?) \text{ لا تكفي عدد الحالات } 2^4 = 16 \Rightarrow 2^5 = 32$$

عدد الحالات = 19 حالة  $\leftarrow$  الترميز على 5 bit

#### معادلات fetch

- 1)  $F_1: AR \leftarrow PC$

- 2)  $F_2: DR \leftarrow M[AR]; PC \leftarrow PC + 1$

- 3)  $F_3: IR \leftarrow DR(op); AR \leftarrow DR(x)$

### عدد مراحل التنفيذ لكل عملية

|                              |                                  |                               |                         |

|------------------------------|----------------------------------|-------------------------------|-------------------------|

| 1) <i>MOV_R</i>              | $R \leftarrow AC$                | 9) <i>STR_ID<sub>2</sub></i>  | $AR \leftarrow DR$      |

| 2) <i>SUB_R</i>              | $AC \leftarrow AC - R$           | 10) <i>STR_ID<sub>3</sub></i> | $DR \leftarrow R$       |

| 3) <i>OR_R</i>               | $AC \leftarrow AC \text{ or } R$ | 11) <i>STR_ID<sub>4</sub></i> | $M[AR] \leftarrow DR$   |

| 4) <i>LDR_D<sub>1</sub></i>  | $DR \leftarrow M[AR]$            | 12) <i>SUB_D<sub>1</sub></i>  | $DR \leftarrow M[AR]$   |

| 5) <i>LDR_D<sub>2</sub></i>  | $R \leftarrow DR$                | 13) <i>SUB_D<sub>2</sub></i>  | $AC \leftarrow AC - DR$ |

| 6) <i>STAC_D<sub>1</sub></i> | $DR \leftarrow AC$               | 14) <i>JMP_D<sub>1</sub></i>  | $DR \leftarrow M[AR]$   |

| 7) <i>STAC_D<sub>2</sub></i> | $M[AR] \leftarrow DR$            | 15) <i>JMP_D<sub>2</sub></i>  | $PC \leftarrow DR(x)$   |

| 8) <i>STR_ID<sub>1</sub></i> | $DR \leftarrow M[AR]$            | 16) <i>NOP</i>                | <i>Do Nothing</i>       |

ولرسم مخطط الحالات سنقوم باستخدام عدداً عوضاً عن القلاب من أجل كل حالة.

#### العمليات التي ستطبقها على العدد

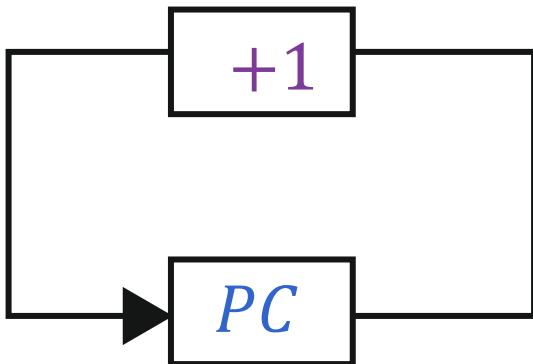

1. **الزيادة بمقدار 1 (increment)** نستخدمها عند الانتقال من حالة إلى أخرى بحيث تكون الحالات متسلسلة

مثل الانتقال من  $F_1 \rightarrow F_2$  حيث عمليات *fetch* متسلسلة وقريبة لا يمكن أن تسبق حالة حالة أخرى، أو

الانتقال من حالة إلى أخرى ضمن نفس التعليمية.

مثال:  $STR\_ID_4 \leftarrow STR\_ID_3, SUB\_D_2 \leftarrow SUB\_D_1$

2. **تحميل قيمة معينة على العدد (load)** تغير قيمة العدد إلى قيمة  $x$  وتستخدم بعد مرحلة  $F_3$  للذهاب

للتعليمية المناسبة إذ لا يمكن إضافة 1 لقيمة ترميز  $F_3$  لوجود 9 حالات مختلفة.

3. **تصفير العدد (Reset)** يستخدم بعد الانتهاء من مراحل التعليمية فيجب علينا العودة إلى  $F_1$  لجلب التعليمية

التالية.

فيكون المخطط النهائي لرسم الحالات مع ترميزها حيث عدد الحالات = 19 حالة والترميز على 5 bit.

ملاحظة: ترميز العمليات فيما بعد  $F_3$  (الـ 9 حالات) اختياري بحيث يمكننا الترميز بأي طريقة منطقية بحيث يكون الترميز مختلف عن حالات  $fetch$  الثلاث وأن تكون مراحل (حالات) التعليمقة الواحدة متسلسلة بزيادة 1 في التعليمات التي فيها أكثر من حالة.

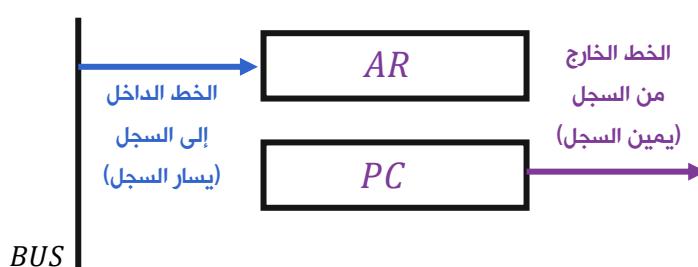

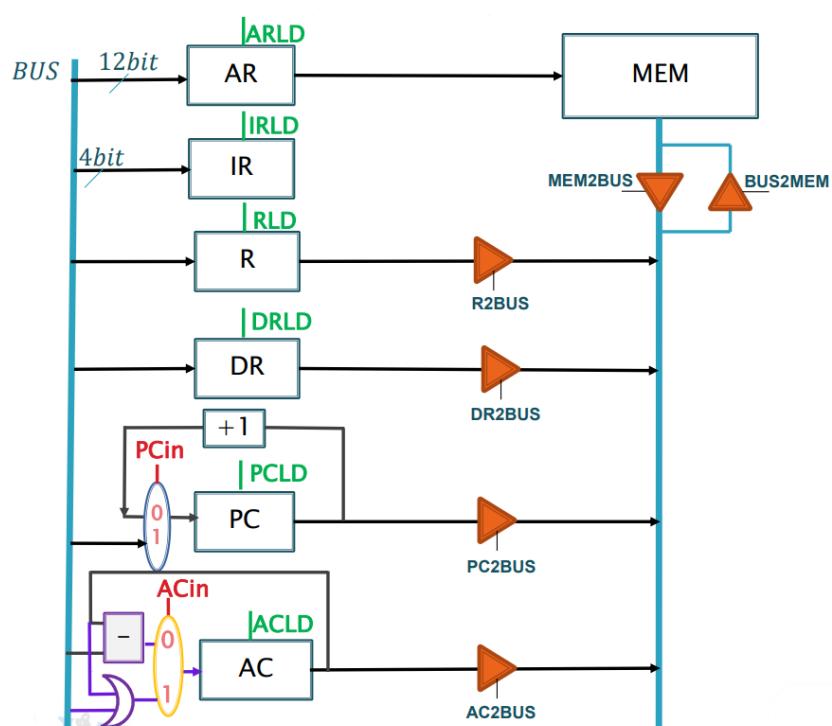

## 5. ارسم ممر المعطيات Data Path وحدد إشارات التحكم المطلوبة ثم استنتج معادلاتها؟

في هذا الطلب سوف نحتاج إلى ثلاثة أجزاء رئيسية قبل البدء بالرسم:

1. السجلات الموجودة في المعالج (  $AR, DR, IR \dots$  ).

2. الذاكرة (  $memory$  ).

3. الـ Bus وهو طريق النقل من وإلى السجلات.

سنقوم بافتراض أن أي عملية نقل يجب أن تحدث باستخدام Bus إذ لا يمكن أن نصل سجلين ببعضهما مباشرةً دون المرور بـ Bus.

سنقوم بالمرور على جميع الحالات الـ 19 ورسم خطوط الوصل من وإلى السجلات.

**مثال** كيفية الوصل باستخدام الـ BUS  $F_1: AR \leftarrow PC$

سنفترض أن الخط الذي على يمين السجل هو الخارج من السجل والخط الذي على يسار السجل هو الداخل إلى السجل فيكون الشكل:

هذا في الحالات العامة ولكن لدينا بعض الحالات الخاصة

- في بعض الحالات لا داعي لخروج التعليمية إلى  $BUS$  إذ يكون التعديل على نفس السجل.

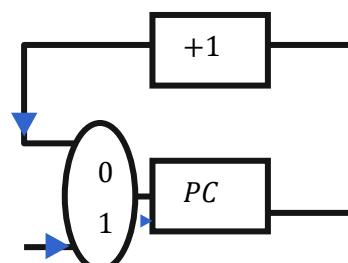

مثال:  $PC \leftarrow PC + 1$

هنا سيكون

هناك خط

داخلي وهو

$R$  فالـ

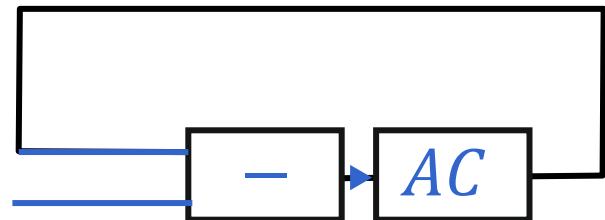

مثال:  $AC \leftarrow AC - R$

أي سنقوم برسم دارة صغيرة في نفس السجل.

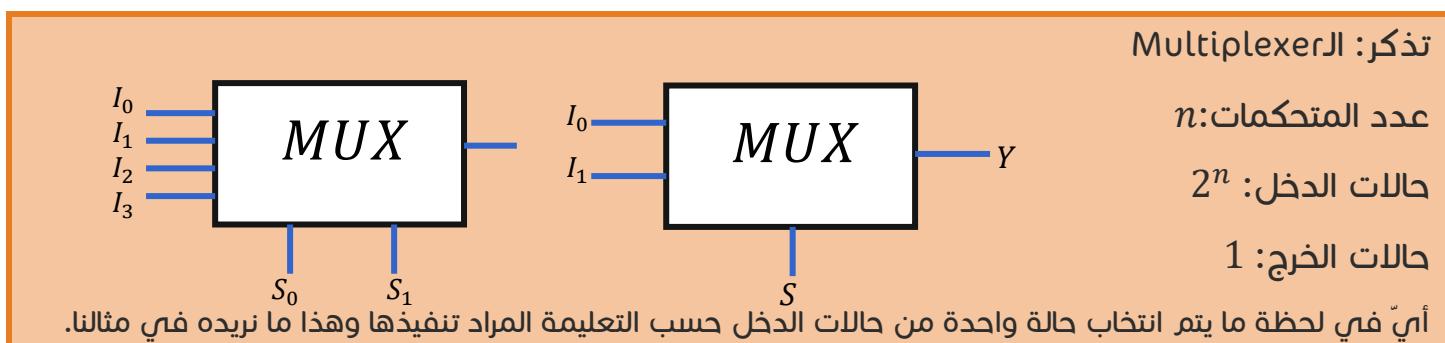

- عند وجود أكثر من دخل إلى نفس السجل يجب علينا استخدام الناخب (Multiplexer) لانتخاب خرج واحد من جميع حالات الدخل.

الآن ما هي السجلات التي تحتاج إلى ناخب؟ ▪

2)  $AC$

$$AC \leftarrow AC - R$$

$$AC \leftarrow A \text{ or } R$$

1)  $PC$

$$PC \leftarrow PC + 1$$

$$PC \leftarrow DR(x)$$

وبعد الانتهاء من رسم جميع خطوط الدخل والخرج يتبقى لدينا مشكلة واحدة وهي أن جميع السجلات موصولة مع  $BUS$  في نفس الوقت لذلك علينا إيجاد آلية لتنظيم دخول وخروج المعلومات من وإلى  $BUS$ .

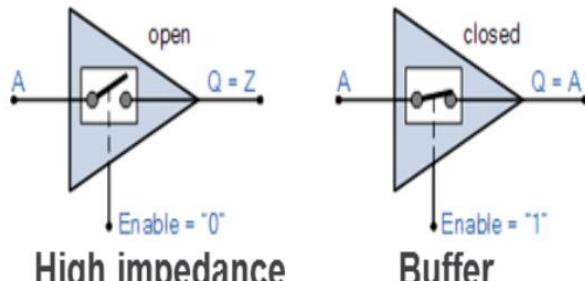

## مشكلة تنظيم خرج السجلات إلى BUS ▪

## Tri-state Buffer

سنقوم باستخدام آلية مشابهة للناخب.

وهي الـ *Tri – State Buffer* وهي عبارة عن قاطع *on/off* فعند لحظة ما نجعل قيمة القاطع 1 (on) عند السجل الذي تتعامل معه في هذه التعليمة وبقى القواطع جميعها 0 (off) وعندما نضمن تنظيم خروج المعلومات إلى الـ *BUS* دون حصول تداخل ونقوم بوضع الـ *Tri – State Buffer* (R, DR, PC, AC) *BUS* عند خرج كل سجل يتصل مع الـ *BUS* وأثنين لتنظيم الدخول من وإلى الذاكرة.

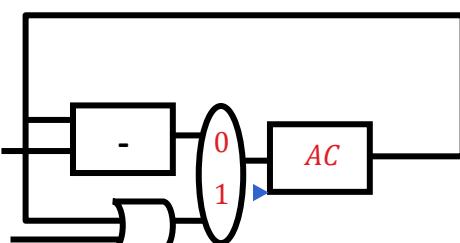

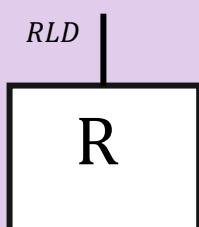

## مشكلة تنظيم دخل السجلات من BUS ▪

هنا سنقوم باستخدام خط تدكم من أجل كل سجل (*load*) و تكون وظيفته هي السماح بالكتابة على السجل أو منع الكتابة عليه (رفض  $\leftarrow 0$ , سماح  $\leftarrow 1$ ) نقوم بإرسال 1 للسجل المراد التغيير عليه حسب التعليمة و 0 للباقي.

ويكون شكله:

ولكن كيف نسميه؟ نضع اسم السجل وبجانبه *(load)**LD*

.*IR*  $\rightarrow$  *IRLD*    *R*  $\rightarrow$  *RLD*    *DR*  $\rightarrow$  *DRLD*

ومنه تكون الرسامة النهائية لعمق المعطيات من الشكل:

- $F_1: AR \leftarrow PC$

- $F_2: DR \leftarrow M[AR]; PC \leftarrow PC + 1$

- $F_3: IR \leftarrow DR(OP); AR \leftarrow DR(X)$

- $MOV R: R \leftarrow AC$

- $SUB R: AC \leftarrow AC - R$

- $OR R: AC \leftarrow AC \text{ or } R$

- $LDR D_1: DR \leftarrow M[AR]$

- $LDR D_2: R \leftarrow DR$

- $STAC D_1: DR \leftarrow AC$

- $STAC D_2: M[AR] \leftarrow DR$

- $STR ID_1: DR \leftarrow M[AR]$

- $STR ID_2: AR \leftarrow DR$

- $STR ID_3: DR \leftarrow R$

- $STR ID_4: M[AR] \leftarrow DR$

- $SUB D_1: DR \leftarrow M[AR]$

- $SUB D_2: AC \leftarrow AC - DR$

- $JMP D_1: DR \leftarrow M[AR]$

- $JMP D_2: PC \leftarrow DR(x)$

- $DO nothing NOP:$

النهاية